Effets de la contre réaction sur les amplificateurs.

Un prolongement du livre « Comprendre l’électronique par la simulation » par S. Dusausay Page 1 sur 17

Effets de la contre réaction sur les amplificateurs.

Des éléments qu’un bon électronicien analogicien doit savoir.

J’invite le lecteur à consulter le livre* (tome 1) et le site** (tome2) pour des informations

complémentaires signalées par [Réf i].

* Comprendre l’électronique par la simulation ** Site Internet personnel,

Serge Dusausay, Vuibert, http://membres.lycos.fr/cepls

402 pages, n° ISBN 2 7117 8952 7

1. Rappels sur le formalisme des systèmes bouclés

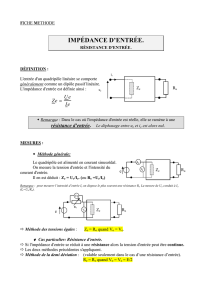

La structure générale d'un système bouclé se représente par 4 "blocs":

On appelle : a(jω), la transmittance d'entrée,

b(jω), la transmittance de retour,

A(jω), la transmittance de la chaîne directe.

Un comparateur réalisant la différence ε = e+ - e-.

Schéma bloc

On peut écrire (par simplicité d’écriture, on omet jω ):

s = A ε avec ε = a e - b s

où A, a, b sont des fonctions complexes. On déduit :

e

s = Ab1

aA

+

Relation générale

Dans le cas (très fréquent, et ce dans une large bande de fréquence) où Ab >> 1, la fonction de transfert

du système bouclé est : e

s≈

b

a.

Ce rapport, appelé fonction de transfert en boucle fermée (F.T.B.F.), est donc rendu indépendant de la

chaîne directe, et est lié essentiellement aux éléments environnants, c’est à dire l’atténuation d’entrée (si

elle existe) et la chaîne de retour.

Le terme (1+ A b) est appelé le facteur de réaction. Il n’a pas de dimension.

Les autres termes, a, b, A peuvent avoir des dimensions différentes, selon les grandeurs de travail en e, s.

Le formalisme des systèmes bouclés est exploité dans de nombreux domaines de la physique.

Mais ce qui va suivre s'applique à des montages électroniques qui peuvent se représenter sous forme de

quadripôles.

Il existe 2 possibilités de branchements (série, parallèle) et 2 accès (entrée, sortie), ce qui forme 4

possibilités de contre réaction, présentées brièvement dans les 4 paragraphes suivants.

Un prolongement du livre « Comprendre l’électronique par la simulation » par S. Dusausay Page 2 sur 17

2. Présentation de principe des 4 cas de contre réaction

Il existe deux terminologies qui rappellent, dans le sens sortie/entrée (convention "automatique"):

- les branchements,

- les grandeurs de sortie et d'entrée du système bouclé.

Cela est rappelé dans l’intitulé des titres des paragraphes.

2.1 Contre réaction à entrée série et à sortie série. (appelé également série/série,

ou courant/tension)

Une tension d'erreur (Vε) attaque un amplificateur de transconductance A.

Le signal de sortie est un courant. La chaîne de retour est un convertisseur courant tension :

ve = vε + vr , soit : vε = ve - vr

A = is/vε

b = vr/is

2.2 Contre réaction à entrée série et sortie parallèle. (appelé également

parallèle/série ou tension/tension)

La maille d'entrée est la même que le cas précédent. La grandeur de sortie est une tension. La branche de

retour délivre une tension vr à partir de la tension vs (exemple : un pont diviseur) :

ve = vε + vr , soit : vε = ve - vr

A = vs/vε

b = vr/vs

2.3 Contre réaction à entrée parallèle et sortie série. (appelé également

série/parallèle ou courant/courant)

L'entrée est un courant, qui est dévié dans une autre branche (ou réinjecté, selon la convention de signe),

par un nœud de courant. La grandeur de sortie est un courant qui traverse également l'entrée de la chaîne

de retour.

ie = iε + ir , soit : iε = ie - ir

A = is/iε

b = ir/is

2.4 Contre réaction à entrée parallèle et sortie parallèle. (appelé également

parallèle/parallèle ou tension/courant)

Un nœud de courant est à l'entrée. La sortie est une tension. La branche de retour délivre une tension vr à

partir de la tension vs (exemple : un pont diviseur).

ie = iε + ir , soit : iε = ie - ir

A = vs/iε

b = ir/vs

Un prolongement du livre « Comprendre l’électronique par la simulation » par S. Dusausay Page 3 sur 17

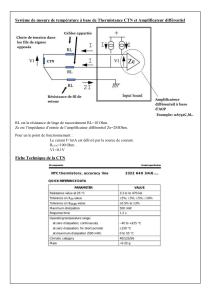

3. Calculs des impédances et de la F.T.B.F. du système bouclé

Pour ces 4 cas de contre réaction, nous allons

utiliser le même amplificateur de tension,

représenté par le quadripôle suivant :

Ri est sa résistance d’entrée,

Ro est sa résistance de sortie

Av son amplification en tension

- Nous allons calculer, pour chaque montage contre-réactionné, et en appliquant les lois de mailles et de

nœuds : l’impédance de sortie (Zs),

l’impédance d’entrée (Ze),

la F.T.B.F., qui est le rapport : grandeur de sortie / grandeur d’entrée.

- De plus, en utilisant le formalisme des systèmes bouclés qui exploite les schémas blocs, on donnera :

la F.T.B.F., l’identification de A et b, paramètres des schémas blocs,

et quelques remarques sur Zs et Ze.

Rappel : (1+Ab) est le facteur de réaction

On rappelle les définitions des impédances :

Ze = ve/ie

Zs = vs/is , la source d’entrée étant inactive (entrée série : ve = 0 ; entrée parallèle : ie = 0).

3.1 Contre réaction à entrée série et à sortie série.

Calcul de l’impédance de sortie :

vs = Av vε + Ro is + uR1, avec vε = Ri ie et uR1 = - vε (car ve = 0)

vs = Av vε + Ro is - vε = Ro is + vε (Av -1)

or vε = - uR1 = - R1 (ie + is)

hypothèse 1 : | ie | << | is |, d’où vε ≈ - R1 is

Il vient : vs = Ro is - R1 is (Av -1) = is [Ro + R1 (1-Av)]

D’où : Zs ≈ Ro + R1 (1-Av) [1]

Calcul de l’impédance d’entrée :

ve = vε + uR1 , avec vε = Ri ie et uR1 = R1 (ie + is) où is = - (Av vε + uR1 ) / (RL+Ro)

hypothèse 2 : |uR1 | << | Av vε |, d’où is ≈ - Av vε / (RL+Ro) ,

et par l’hypothèse 1, uR1 ≈ R1 is ≈ - R1 [Av vε / (RL+Ro) ] = - R1 [Av Ri ie / (RL+Ro)]

Par conséquence : ve ≈ Ri ie - R1 (Av Ri ie / (RL+Ro) ) = ie [Ri - R1 (Av Ri / (RL+Ro)) ]

D’où :

+

−≈ RoR

R A

1Ri Ze

L

1v [2] Remarque : avec |Av R1| >> (RL+Ro), on a RoR

R A

Ri Ze

L

1v

+

−≈ [2’]

Remarque importante : il est clair que pour avoir des impédances d’entrée et de sortie positives, il faut

avoir le coefficient d’amplification Av < 0 .

Calcul de is/ve :

On reprend l’hypothèse 1 : | ie | << | is |, d’où is ≈ - Av vε / (R1+Ro+RL) par loi des mailles

vε = ve - uR1 = ve - R1 (ie +is) ≈ ve - R1 is toujours par hypothèse 1.

d’où is ≈ - Av (ve - R1 is) / (R1+Ro+RL). Après développement :

1vL

v

e

s

)RA(1RRo

A

v

i

−++

≈ [3]

Remarque : si (1-Av)R1 >> Ro + RL et | Av | >> 1, on a

1e

s

R

1

v

i−≈ . [4]

Un prolongement du livre « Comprendre l’électronique par la simulation » par S. Dusausay Page 4 sur 17

Calcul de is/ve par les schémas blocs :

b = vr/is = uR1/is . Or uR1 = R1 (ie+is) ≈ R1 is par l’hypothèse 1. D’où b ≈ R1 .

Si Ab >> 1, la FTBF =

1e

s

R

1

b

1

Ab1

A

v

i=≈

+

= [4]

Remarque intéressante :

A = is/vε , soit d’après le calcul précédent exploitant l’hypothèse 2 : A ≈ - Av / (Ro+RL)

On peut écrire : Ab ≈ - Av R1 / (Ro+RL)

Il vient que la relation [2] s’écrit Ze ≈ Ri (1+Ab). Ri est multipliée par le facteur de réaction.

3.2 Contre réaction à entrée série et sortie parallèle.

Calcul de l’impédance de sortie :

vs = Av vε + Ro (is+ i2) Posons R11 = R1//Ri (ve = 0)

i2 = - vs / (R2+R11) et vε = - uR1= - vs R11 / (R2+R11) par pont diviseur

D’où vs = - Av vs R11 / (R2+R11) + Ro is - Ro vs / (R2+R11)

soit Zs =

112112

11v

RR

Ro

RR

R A

1

Ro

+

+

+

+

<< Ro. [1]

Calcul de l’impédance d’entrée :

ve = vε + uR1 , avec vε = Ri ie et uR1 = R1 (ie – i2) où i2 = (uR1 - vs) / R2

hypothèse 1 : | Ro (is + i2)| << | vs |, d’où vs ≈ Av vε d’où : i2 ≈ (uR1 - Av vε ) / R2

=> uR1 = R1 ie – R1 i2 ≈ R1 ie – (R1/R2) uR1 + (R1/R2)Av vε

d’où uR1 ≈ ie R1R2/(R1+R2) + Av vε R1/(R1+R2)

soit, mis dans l’équation de départ : ve ≈ Ri ie + ie R1R2/(R1+R2) + Av Ri ie R1/(R1+R2)

permet d’avoir Ze ≈ Ri A

RR

R

RR

RR

Ri v

21

1

21

21

+

+

+

+ ≈ )A

RR

R

1(Ri v

21

1

+

+

Calcul de vs/ve :

On reprend l’hypothèse 1 : | Ro (is + i2)| << | vs |, d’où vs ≈ Av vε . De plus, ve = vε + uR1

hypothèse 2 : |ie | << | i2|, d’où uR1 ≈ vs R1/(R1+R2) soit ve ≈ vs/Av + vs R1/(R1+R2)

d’où

121

21v

e

s

RA RR

)R(R A

v

v

++

+

≈ si Av R1 >> R1+R2

1

2

e

s

R

R

1

v

v+≈ [2]

Calcul de vs/ve par les schémas blocs

b = vr/vs = uR1/vs , soit en reprenant l’hypothèse 2 : |ie | << | i2|, d’où b ≈ R1/(R1+R2)

Si Ab >> 1, la FTBF =

1

2

e

s

R

R

1

b

1

Ab1

A

v

v+=≈

+

=

Remarque intéressante :

A = vs/vε , soit en reprenant l’hypothèse 1 : | Ro (is + i2)| << | vs |, A ≈ Av

Nous avons donc : A b ≈ Av R1/(R1+R2)

Si Ri >> R1, soit R11 = R1 et Ro << (R2+R11), on a Zs ≈

12

1v

RR

R A

1

Ro

+

+

Qui s’écrit également Ro /(1+Ab) : Ro est divisée par le facteur de réaction. [1’]

De même, Ze ≈ Ri (1+Ab). [3] : Ri est multipliée par le facteur de réaction.

Un prolongement du livre « Comprendre l’électronique par la simulation » par S. Dusausay Page 5 sur 17

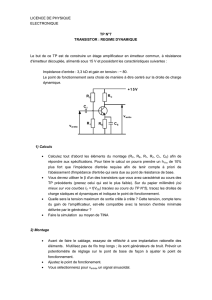

Remarque intéressante :

Le montage amplificateur non inverseur à base d’amplificateur opérationnel est le schéma type de la

contre réaction entrée série sortie parallèle.

1

2

e

s

R

R

1

v

v+=

On a, pour l’amplificateur seul :

Ri : en bipolaire, JFET : du MOhm au GOhm. En CMOS : de l’ordre du TOhm

Ro : en bipolaire : classiquement quelques ohms à 50 ohms (si résistance interne de

protection intégrée). En CMOS : quelques kOhm.

Av de l’ordre de 105 à 106 en basse fréquence.

Les hypothèses 1 et 2 de ce paragraphe sont largement vérifiées.

Il s’ensuit que, dans ce type de montage :

Ze ≈ Ri A

RR

R

v

21

1

+ donc quasiment infini (Ze ≈ Av Ri pour un suiveur)

Zs ≈

12

1v

RR

R A

1

Ro

+

+

Donnons un ordre de grandeur : avec Ro = 50 Ohm et Av = 105 on a :

Zs = 50 mOhm pour un montage amplificateur par 100,

ou 500microOhm pour un suiveur.

Dans ce montage, Zs est quasiment nulle.

3.3 Contre réaction à entrée parallèle et sortie série.

Calcul de l’impédance de sortie :

vs = Av vε + Ro is + uR1

uR1 = REQ is avec REQ = R1 // (R2+Ri), car ie = 0

Or vε = uR1 Ri/(Ri+R2) par pont diviseur

Soit vs = Av REQ is Ri/(Ri+R2) + Ro is + REQ is

D’où Zs = )

RRi

Ri

A (1 RRo

2

vEQ +

++ [1]

Remarque : si R2 + Ri >> R1 , on a REQ ≈ R1

Et si Ri >> R2 et avec Av >> 1, on aboutit à : Zs ≈ Ro + Av R1 [1’]

Sous cette forme, on identifie mieux le rôle prépondérant de R1 dans Zs.

Calcul de l’impédance d’entrée : calculons l’admittance d’entrée ie / ve :

Par la loi des nœuds ie = iε + i2, et par ve = vε on a : ie / ve = iε / vε + i2 / vε

Or iε / vε est 1/Ri. , et i2 = (vε - uR1 ) /R2 .

Hypothèse 1 : | i2 | << | is | d’où uR1 = - Av vε R1/ (Ro + RL + R1) par pont diviseur

i2 = vε/R2 + Av vε R1/R2(Ro+RL+R1) en conséquence i2 / vε = 1/R2 + AvR1/R2(Ro+RL+R1)

L’admittance d’entrée : ie / ve = 1/Ri + 1/R2 + AvR1/R2(Ro+RL+R1)

Ce qui signifie que l’impédance d’entrée est : Ze ≈

1v

1L2

2RA

)RR(RoR

//R// ++

Ri [2]

Calcul de is/ie :

La maille d’entrée donne : ve = Ri iε = Ri (ie - i2) = Ri ie - Ri i2 [a]

Également : ve = R2 i2 + uR1

En exploitant l’hypothèse 1 : | i2 | << | is | , uR1 ≈ R1 is d’où ve ≈ R2 i2 + R1 is [b]

En écrivant [a] = [b] Ri ie - Ri i2 = R2 i2 + R1 is

On déduit i2 = Ri R

i Ri Ri

2

s1e

+

−mis dans [b] donne

()

s 1s 1e

2

2iRiRi Ri

Ri R

R

ve +−

+

= [c]

La maille de sortie donne : vs = - RL is = Av vε + Ro is + uR1 ≈ Av ve + Ro is + R1 is

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

1

/

17

100%