Circuits logiques combinatoires: Codeurs, Décodeurs, Multiplexeurs

Telechargé par

younessifrah4

Chapitre 4 : Circuits logiques combinatoires

Un circuit est dit combinatoire si sa sortie ne dépend que de la combinaison de ses entrées. En

particulier, la variable temps n’intervient pas dans la détermination de l’état des sorties (au

contraire des circuits séquentiels) ; le circuit ne conserve aucune mémoire de l’état précédent.

1) Codeur binaire :

Rôle : traduire un certain nombre de chiffres décimaux en binaire.

3 CPS

3 CPS

Circuit

combinatoire

E0

E1

En

S0

Sp

2n entrées

mais 1 seule 0

active à la fois 1

2

3

A0

A1 n sorties

Codeur

Entrées Sorties

x3 x2 x1 x0 A1 A0

3 2 1 0

0 0 0 1 0 0

0 0 1 0 0 1

0 1 0 0 1 0

1 0 0 0 1 1

- 0 - 1

0 - - -

- - - -

1 - - -

1 0

0 1

0

x1 x0 00 01 11 10

x3 x2

00

01

11

10

- 0 - 0

1 - - -

- - - -

1 - - -

1 0

0 1

0

x1 x0 00 01 11 10

x3 x2

00

01

11

10

A0 = x2 x0

ou

A0 = x3 + x1

A1 = x1 x0

ou

A1 = x3 + x2

2) Décodeur binaire :

Rôle : décoder une information binaire.

S0 = E1 E0

S1 = E1 E0

S2 = E1 E0 S3 = E1 E0

E1 E0 00 01 11 10

S0 = E1 E0

3) Transcodeur :

Rôle : passer d’un code à un autre

Exemple :

E1 E0 00 01 11 10

E2

0

1

E1 E0 00 01 11 10

E2

0

1

E1 E0 00 01 11 10

E2

0

1

2n sorties

mais 1 seule

active à la fois

n entrées

E0

E1

Décodeur

S0

S1

S2

S3

Entrées Sorties

E1 E0 S3 S2 S1 S0

0 0 0 0 0 1

0 1 0 0 1 0

1 0 0 1 0 0

1 1 1 0 0 0

Transcodeur

E0

E1

E2

S0

S1

S2

Entrées Sorties

E2 E1 E0 S2 S1 S0

0 0 0 0 0 0

0 0 1 0 0 1

0 1 0 0 1 1

0 1 1 0 1 0

1 0 0 1 1 0

1 0 1 1 1 1

1 1 0 1 0 1

1 1 1 1 0 0

Binaire

naturel

Binaire

réfléchi

0 1 0 1

0 1 0 1

0 0 1 1

1 1 0 0

0 0 0 0

1 1 1 1

S0 = E1 E0 + E1 E0 = E1 + E0

2 CPP

S1 = E2 E1 + E2 E1 = E1 + E2

2 CPP

1 CPP

S2 = E2

1 0 0 0

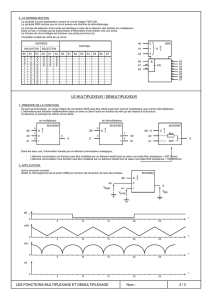

4) Multiplexeur :

V = 0 S = 0 l’adresse appliquée et les entrées d’informations

V = 1 S = état de l’entrée d’informations adressée

A2 A1 A0 E0 E1 ……………………………………….. E7 S

0 0 0 x x x E0

0 0 1 x x x E1

0 1 0 x x x E2

1 1 1 x x x E7

S = E0 A2 A1 A0 + E1 A2 A1 A0 + E2 A2 A1 A0 + ………….. …….. + E7 A2 A1 A0

Rôles :

- connaître l’état d’une entrée d’informations

- aiguilleur

- conversion // série

- générateur de fonction

Multiplexeur

E0 E1 ……………………………………….. E7

n entrées A2

adresses A1

A0

Entrée

validation

V

S

2n entrées

d’informations

aiguilleur

conversion // série

E0 E1 ………………………………………. E7

Multiplexeur

E0 E1 ……………………………………….. E7

n entrées A2

adresses A1

A0

Entrée

validation

V

S

E

circuit

Multiplexeur

n entrées A2

adresses A1

A0

Entrée

validation

V

S

E

système série

système parallèle

générateur de fonction

exemple :

A l’aide d’un multiplexeur à 2 entrées adresses et 4 entrées d’information, générer la fonction

F suivante : F(x0 , x1 , x2) = x0+ x1 x2

A1 A0 S

0 0 E0

0 1 E1

1 0 E2

1 1 E3

S = E0 A1 A0 + E1 A1 A0 + E2 A1 A0 + E3 A1 A0

On doit tout d’abord écrire l’expression de F sous forme canonique (en faisant apparaître

toutes les variables dans chaque monôme de l’expression)

F(x0 , x1 , x2) = x0+ x1 x2 = x0 (x1 + x1)+ x1 x2 (x0 + x0)

= x0 x1 + x0 x1 + x1 x2 x0 + x1 x2 x0

= x0 x1(x2 + x2) + x0 x1 (x2 + x2) + x1 x2 x0 + x1 x2 x0

= x0 x1 x2 + x0 x1 x2 + x0 x1 x2 + x0 x1 x2 + x1 x2 x0 + x1 x2 x0

Ensuite on va appliquer, sur les entrées adresses du multiplexeur, 2 variables de la fonction F :

A0 = x0 et A1 = x1 S = E0 x1 x 0 + E1 x1 x0 + E2 x1 x0 + E3 x1 x0

Ensuite, on identifie F à S , d’où :

E0 x1 x 0 = x0 x1 x2 + x0 x1 x2 = x0 x1 (x2 + x2) E0 = x2 + x2 = 1

E1 x1 x0 = 0 E1 = 0

E2 x1 x0 = x0 x1 x2 + x0 x1 x2 + x0 x1 x2

= x0 x1 (x2 + x2 + x2) E2 = 1

E3 x1 x0 = x0 x1 x2 E3 = x2

Multiplexeur

E0 E1 E2 E3

A1

A0

S

A1 E0 E1 E2 E3

A0 Multiplexeur

S

1 0 1 x2

x1

x0

F = x0 + x1 x2

6

6

7

7

8

8

9

9

1

/

9

100%