Correction TD2

EXERCICE1 : PCF8574

La communication I2C avec ce périphérique est initiée par un maître qui envoie une

condition de démarrage, une transition haut-bas sur l'E/S SDA alors que l'entrée SCL

est haute. Après la condition de démarrage, l'octet d'adresse de périphérique est

envoyé, bit important (MSB) en premier, y compris le bit de direction de données

(R/W). Cet appareil ne répond pas à l'adresse générale de l'appel. Après la réception

de l'octet d'adresse valide, ce périphérique répond avec un accusé de réception, une

valeur faible sur l'E/S SDA pendant le plus fort de l'impulsion d'horloge liée à

l'accusé de réception. Les entrées d'adresse (A0-A2) de l'équipement esclave ne

doivent pas être changées entre les conditions de démarrage et d'arrêt.

L'octet de données suit l'acquittement d'adresse. Si le bit R/W est élevé, les données

de ce périphérique sont les valeurs lues sur le port P. Si le bit R/W est faible, les

données proviennent du maître et doivent être transmises au port P. L'octet de

données est suivi d'un accusé de réception envoyé par cet appareil. Si d'autres octets

de données sont envoyés par le maître, après l'acquittement, ils sont ignorés par ce

périphérique. Les données sont sorties uniquement si des octets complets sont reçus

et acquittés. Les données de sortie seront valides à l'instant, tpv, après la transition

bas-haut de SCL et pendant le cycle d'horloge pour l'acquittement.

Une condition d'arrêt, qui est une transition de bas à haut sur l'E/S SDA alors que

l'entrée SCL est haute, est envoyée par le maîtriser.

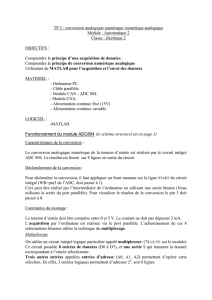

EXERCICE 2 : PCF8591

Le PCF8591 est un dispositif d'acquisition de données CMOS 8 bits, monopuce, basse

consommation, à alimentation simple, avec quatre entrées analogiques, une sortie

analogique et une interface bus I2C série. Trois broches d'adresse A0, A1 et A2 sont

utilisées pour programmer l'adresse matérielle, ce qui permet d'utiliser jusqu'à huit

périphériques connectés au bus I2C sans matériel supplémentaire.

L'adresse, le contrôle et les données vers et depuis l'appareil sont transférés en série

via le bus I2C bidirectionnel à deux lignes.

Les fonctions du dispositif comprennent un multiplexage d'entrée analogique, une

fonction de poursuite et de maintien sur puce, une conversion analogique-numérique

de 8 bits et une conversion numérique-analogique de 8 bits. Le taux de conversion

maximum est donné par la vitesse maximale du bus I2C.

Adressage

Chaque appareil PCF8591 dans un système de bus I2C est activé en envoyant une

adresse valide à l'appareil. L'adresse est constituée d'une partie fixe et d'une partie

programmable. La partie programmable doit être réglée en fonction des broches

d'adresse A0, A1 et A2.

L'adresse est toujours envoyée en tant que premier octet après la condition de

démarrage dans le protocole de bus I2C. Le dernier bit de l'octet d'adresse est le bit

de lecture / écriture qui définit la direction du transfert de données suivant (voir

Tableau 5 à la page 13, Figure 15 à la page 13 et Figure 16 à la page 13).

Octet de contrôle

Le deuxième octet envoyé à un périphérique PCF8591 est stocké dans son registre de

contrôle et est requis pour contrôler la fonction du périphérique.

Le quartet supérieur du registre de contrôle est utilisé pour activer la sortie

analogique et pour programmer les entrées analogiques comme entrées asymétriques

ou différentielles. Le quartet inférieur sélectionne l'un des canaux d'entrée

analogiques définis par le quartet supérieur (voir Figure 4). Si l'indicateur

d'incrémentation automatique est activé, le numéro de canal est incrémenté

automatiquement après chaque conversion A / N.

Si le mode d'incrémentation automatique est souhaité dans les applications où

l'oscillateur interne est utilisé, le drapeau de validation de sortie analogique doit être

défini dans l'octet de contrôle (bit 6). Cela permet à l'oscillateur interne de

fonctionner en continu, empêchant ainsi les erreurs de conversion résultant du délai

de démarrage de l'oscillateur. Le drapeau de validation de sortie analogique peut

être réinitialisé à d'autres moments pour réduire la consommation d'énergie au

repos.

La sélection d'un canal d'entrée inexistant entraîne l'attribution du numéro de canal

disponible le plus élevé. Par conséquent, si l'indicateur d'incrémentation

automatique est activé, le canal sélectionné suivant est toujours le canal 0. Les bits les

plus significatifs des deux quartets sont réservés aux futures fonctions possibles et

doivent être mis à 0 logique. Après une réinitialisation à la mise sous tension (POR)

Dans ce cas, tous les bits du registre de contrôle sont remis à 0. Le convertisseur N /

A et l'oscillateur sont désactivés pour économiser l'énergie. La sortie analogique est

commutée sur un état de haute impédance

Conversion D / A

Le troisième octet envoyé à un dispositif PCF8591 est stocké dans le registre de

données DAC et est converti en la tension analogique correspondante en utilisant le

convertisseur N / A sur puce. Ce convertisseur N / A se compose d'une chaîne de

diviseur de résistance connectée à la tension de référence externe avec 256 prises et

commutateurs de sélection. Le décodeur de prises commute l'une de ces prises sur la

ligne de sortie du CNA (voir la figure 5).

La tension de sortie analogique est tamponnée par un amplificateur à gain unitaire à

mise à zéro automatique. Le réglage du drapeau de validation de sortie analogique

du registre de contrôle active ou désactive cet amplificateur tampon. Dans l'état actif,

la tension de sortie est maintenue jusqu'à ce qu'un autre octet de données soit

envoyé.

Le convertisseur N / A sur puce est également utilisé pour la conversion A / N en

approximation successive. Afin de libérer le DAC pour un cycle de conversion A /

N, l'amplificateur à gain unitaire est équipé d'un circuit de poursuite et de maintien.

Ce circuit maintient la tension de sortie pendant l'exécution de la conversion A / N.

Tension de référence

Pour la conversion D / A et A / D, une référence de tension externe stable ou la

tension d'alimentation doit être appliquée à la chaîne du diviseur de résistance

(broches VREF et AGND). La broche AGND doit être connectée à la masse

analogique du système. Il peut avoir un décalage DC en référence à VSS.

Une basse fréquence peut être appliquée aux broches VREF et AGND. Cela permet

l'utilisation du convertisseur N / A en tant que multiplicateur à un quadrant (voir la

section 10 et la figure 6)

Le convertisseur A / N peut également être utilisé comme un diviseur analogique à

un ou deux quadrants. La tension d'entrée analogique est divisée par la tension de

référence. Le résultat est converti en un code binaire. Dans cette application, la

tension de référence doit rester stable pendant le cycle de conversion.

Oscillateur

Un oscillateur sur puce génère le signal d'horloge requis pour le cycle de conversion

A / N et pour rafraîchir l'amplificateur tampon à mise à zéro automatique. Lors de

l'utilisation de cet oscillateur, la broche EXT doit être connectée à VSS. La fréquence

de l'oscillateur est disponible sur la broche OSC. Si la broche EXT est connectée à

VDD, la sortie de l'oscillateur OSC est commutée sur un état haute impédance

permettant d'envoyer un signal d'horloge externe à OSC.

Le bus I2C est destiné à la communication bidirectionnelle à deux lignes entre

différents circuits intégrés ou modules.

Les deux lignes sont une ligne Serial DAta (SDA) et une ligne Serial CLock (SCL). Les

deux lignes doivent être connectées à une alimentation positive via une résistance de

pull-up. Le transfert de données peut être initié uniquement lorsque le bus n'est pas

occupé.

Les entrées doivent être connectées à VSS ou VDD lorsqu'elles ne sont pas utilisées.

Les entrées analogiques peuvent également être connectées à AGND ou VREF.

Afin d'éviter les bruits de masse et d'alimentation excessifs et de réduire au

minimum la diaphonie entre les voies de signaux numériques et analogiques, la

disposition des cartes de circuits imprimés doit être conçue avec soin. Les lignes

d'alimentation communes à un périphérique PCF8591 et les circuits numériques

bruyants et les boucles de masse doivent être évitées. Des condensateurs de

découplage (> 10 µF) sont recommandés pour les entrées d'alimentation et de tension

de référence.

vcc: alim ou niveau logique haut pour un circuit TTL

vdd: alim ou niveau logique haut pour un circuit CMOS

gnd: masse ou niveau logique bas pour un circuit TTL

vss: masse ou niveau logique bas pour un circuit CMOS

6

6

7

7

1

/

7

100%