RÉPUBLIQUE ALGÉRIENNE DÉMOCRATIQUE ET POPULAIRE

MINISTÈRE DE L’ENSEIGNEMENT SUPÉRIEURE ET DE LA RECHERCHE

SCIENTIFIQUE

ÉCOLE NATIONALE POLYTECHNIQUE D’ORAN

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

TP: 02

PROGRAMMATION DES TIMERS

Année universitaire : 2018/2019.

1

Introduction :

Les timers sont en fait des compteurs formés généralement d’un pré-diviseur suivi

d’un registre compteur de 8 ou 16 bits. L’entrée d’horloge peut être interne (mode

timer) ou externe (mode compteur d’évènements). Lorsque le registre compteur

atteint sa valeur maximale et repasse à 0, un bit indicateur (flag) sera positionné et

une interruption pourra être générée, informant aussi la CPU du débordement devra

être remis à 0 après chaque debordement.

Objectifs de ce TP :

Comprendre les modes de fonctionnement des Timers.

Mettre en œuvre les interruptions des Timers en assembleur et en MikroC .

Travail demandé :

Préparation:

La fréquence de Quartez est : Fosc = 8 MHz.

1- Les fréquences maximales de débordement des différents Timers :

On a Fosc = 8MHZ TH =

=

s = 0.5 µs.

Pour le Timer 0 :

TF0 =

Avec: DIV = 256 (PS2 PS1 PS0 =111).

N=0.

Pour le Timer 1 :

TF1 =

Avec: DIV = 8 (T1CKPS1 T1CKPS0 =11).

N=0.

TF0 = 3.27 ms

TF1 = 262.144 ms

2

Pour le Timer 2 :

TF2=DIV1

Avec: DIV1=16 (T2CKPS1 T2CKPS0 =1x) .

DIV2=16 (TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 =1111).

P : valeur placé dans le registre PR2 (P= 255).

Tsy : période de l’horloge système (Tsy =0.5µs).

2- On veut configurer l’un des Timers pour qu’il déborde toutes les 20 ms.

2.1. Le mode de fonctionnement à choisir est : le mode Timer.

2.2. Les valeurs à charger dans les registres :

Timer 0 :

Prediv= 256 (PS2 PS1 PS0 =111).

TMR0 = (0X64).

OPTION_REG= 00000111 = 0X07.

Timer 1 :

Prediv= 1 (T1CKPS1 T1CKPS0 =00).

TMR1L= 0XC0 .

TMR1H= 0X63 .

T1CON= 0X31 .

Timer 2 :

Prediv=DIV1=16 .

Postdiv=DIV2=16.

PR2 = P = 0X9B.

T2CON = 0x7E.

TF2 = 32.76 ms

3

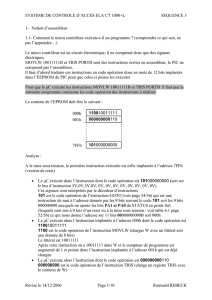

Manipulation:

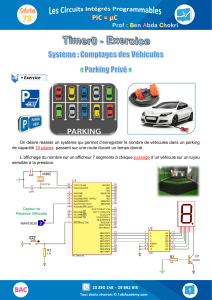

Le mode Timer :

schéma sous proteus

4

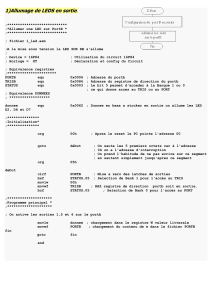

1. Le programme assembleur qui permet de clignoter la LED RB2 toutes les

20ms en utilisant le Timer0 en mode scrutation :

;====================================================================

#include p16f877a.inc ; Include register definition file

__config 0x3F3A

;====================================================================

; VARIABLES

;====================================================================

;====================================================================

; RESET and INTERRUPT VECTORS

;====================================================================

; Reset Vector

RST code 0x0

goto Start

;====================================================================

; CODE SEGMENT

;====================================================================

PGM code

Start

BANKSEL TRISB

BCF TRISB,2

CLRF INTCON

MOVLW 0x07

MOVWF OPTION_REG

BANKSEL PORTB

CLRF PORTB

MOVLW 0X64

MOVWF TMR0

; Write your code here

Loop

MOVLW 0X64

MOVWF TMR0

A1 BTFSS INTCON,2

goto A1

COMF PORTB,1

BCF INTCON,2

goto Loop

;====================================================================

END

6

6

7

7

8

8

9

9

10

10

1

/

10

100%