1 | P a g e

Fonctionnement des microprocesseurs :

Exemple d’Architecture du microprocesseur : 6809

1. Principe de fonctionnement :

1.1. Machine de Von Neumann

1.1.1. Principe

Von Neumann propose en 1945 un principe d’architecture, modèle de

base pour un ordinateur qui

utilise une structure de stockage

unique pour conserver à la fois

les instructions et les données

requises ou générées par le

calcul.

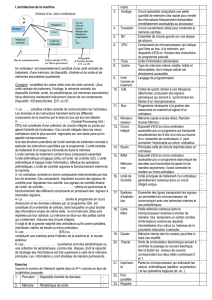

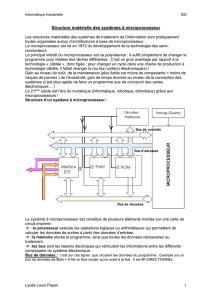

1.1.2. Architecture

L'architecture de Von

Neumann est une circuiterie implémentant un ordinateur universel

contenant les composants suivants :

•

Une unité arithmétique et logique qui procède à des

opérations de calcul et des opérations logiques.

•

Une unité de contrôle qui pilote l'exécution des programmes.

•

Une mémoire dans laquelle sont stockés les programmes et les

données.

•

Une unité d'entrée qui permet l'acquisition de données en

provenance du monde extérieur.

•

Une unité de sortie qui permet l'envoi de résultats à destination

du monde extérieur.

1.2. Architectures CISC et RISC

Un microprocesseur à jeu d'instruction étendu, ou complex

instruction set computer (CISC) en anglais, désigne un

microprocesseur possédant un jeu d'instructions comprenant de

très nombreuses instructions mixées à des modes d'adressages

complexes (plusieurs cycles d'horloge).

Le microprocesseur à jeu d'instruction réduit (RISC)ou

reduced instruction-set computer en anglais est une architecture

matérielle de microprocesseurs. On l'a opposé à la fin des années

1980 et au début des années 1990 à l'architecture CISC (complex

instruction-set computer). La sortie d'architectures hybrides

comme le Pentium (CISC émulé par du RISC) a mis fin, par

disparition de repères.

2. Structure interne d’un microprocesseur

Architecture simplifiée d'un processeur central

➢

L'unité de contrôle (en anglais : Control Unit - CU) est la partie la

2 | P a g e

Fonctionnement des microprocesseurs :

Exemple d’Architecture du microprocesseur : 6809

plus complexe du processeur. Elle se décompose en plusieurs parties

dont elle doit assurer la coordination :

▪

Le processeur exécute une à une les instructions stockées dans

la mémoire centrale. Pour cela, les instructions doivent être

chargées dans le processeur. Elles le sont dans le registre

d'instruction. Ce dernier contient donc l'instruction courante à

exécuter.

▪

L'instruction à exécuter, chargée dans le registre d'instruction,

est interprétée par le décodeur.

▪

Le séquenceur est alors capable d'ordonnancer les diverses

opérations élémentaires du processeur, nécessaires pour exécuter

l'instruction, grâce à un microprogramme.

▪

Le compteur ordinal est un registre particulier qui contient à tout

instant, l'adresse de l'instruction suivante à exécuter.

▪

L'horloge est un dispositif qui détermine le rythme dans lequel sont

exécutées les instructions. Elle fournit un signal régulier au

processeur.

▪

Le registre d'état est, comme le compteur ordinal, un registre

particulier. Il représente à tout moment l'état du processeur. En

effet, divers évènements peuvent créer des situations «

exceptionnelles ». Par exemple, l'addition de deux valeurs peut

dépasser les capacités de représentation du processeur. Dans ce

cas, un bit du registre d'état signale que le processeur est dans l'état

« overflow ».

➢

L'unité de calcul, comme son nom l'indique, effectue tous les calculs

au sein du processeur. À côté des opérations arithmétiques, elle

peut aussi procéder à des opérations logiques. C'est grâce à cette

fonctionnalité que l'ordinateur est capable d'exécuter des

structures de contrôle contenant des conditions

▪

L'accumulateur est le registre de calcul par excellence. C'est

par lui en effet que transitent toutes les données devant faire

l'objet d'une opération ainsi que tous les résultats produits par

calcul arithmétique.

▪

Comme ces opérations mettent généralement en jeu plusieurs

termes et/ou états intermédiaires, l'accumulateur est secondé

par un nombre variable de registres généraux destinés à la

réalisation matérielle des calculs.

▪

ALU : Comme son nom l'indique, l'unité arithmétique et logique

(en anglais : Arithmetic and Logic Unit - ALU) se charge de réaliser

les opérations arithmétiques et logiques.

Pour communiquer avec son environnement, le processeur dispose d'un

ensemble de « bus » :

▪

Le bus d'adresses permet au processeur de désigner l'adresse d'un

octet en mémoire. Selon le cas, il peut s'agir de l'adresse d'un ou

de plusieurs octets à charger dans le processeur ou à stocker en

mémoire.

▪

Le bus de données permet de désigner la valeur à charger dans le

processeur ou à stocker en mémoire.

▪

Enfin, le bus de commande permet au processeur de désigner

l'opération à effectuer, chargement dans le processeur ou stockage

en mémoire.

Exemple d’Architecture du microprocesseur : 6809

3 | P a g e

Fonctionnement des microprocesseurs :

Exemple d’Architecture du microprocesseur : 6809

Le microprocesseur 6809 est un processeur 8 bits dont l'organisation

interne est orientée 16 bits. Il est fabriqué en technologie MOS

(Metal Oxyde Semiconductor)canal N et se présente sous la forme

d'un boîtier DIL (Dual In Line) 40 broches. Il est monotension(5V). Il

existe deux versions différenciées par l'horloge.

le 6809 est rythmé par une horloge interne (f=1 MHZ, 1.5 MHZ et

2MHZ).

Le 6809E est rythmé par une horloge externe.

Ce dernier est adapté aux applications multiprocesseur. Il présente

la particularité de pouvoir être synchronisé par une horloge

extérieure. Compatibilité complète entre les 2 versions.

Le bus des données 8 bits (Do à D7)

Ces huit broches sont bidirectionnelles. Elles permettent la

communication avec le bus des données interne du microprocesseur.

Chaque broche peut "piloter" 1 charge TTL (Transistor-Transistor Logic)

et 8 entrées de circuits appartenant à la famille 680 0. Bus en logique 3

états.

Le bus des adresses 16 bits (A0 à A15 )

Ces broches unidirectionnelles transfèrent l'adresse 16 bits fournie par

le microprocesseur au bus d'adresse du système. Mêmes

caractéristiques électriques que pour le bus des données. Bus en logique

3 états. les adresses sont validées sur le front montant de Q.

Le bus de contrôle

La broche Read/Write. Cette broche indique le sens de transfert des

données sur le bus des données. Ligne à logique 3 états.

R/W = 1 lecture en cours (D0 - D7 sont des entrées) R/W = 0 écriture en

cours (D0 - D7 sont des sorties) Cette ligne est validée sur le front montant

de Q.

Les lignes d'état du bus :

BA (Bus available) et BS (Bus state)

Information qui permet de connaître l'état du microprocesseur à tout

moment.

4 | P a g e

Fonctionnement des microprocesseurs :

Exemple d’Architecture du microprocesseur : 6809

1er cas :

Le microprocesseur est en fonctionnement normal, il gère les bus

d'adresses et de données.

2ème cas :

le microprocesseur est en phase de reconnaissance d'interruption

pendant deux cycles. Cet état

correspond à la recherche des vecteurs d'interruption : Reset, NMI, IRQ,

SW1,2 et 3.

3ème cas :

Ce signal apparaît lorsque le microprocesseur rencontre l'instruction de

synchronisation externe (niveau bas sur SYNC). Il attend alors cette

synchronisation sur une des lignes d'interruption. Les bus sont en haute

impédance pendant ce temps.

Dernier cas :

Correspond à l'arrêt du microprocesseur (niveau bas sur HALT). Le

microprocesseur laisse la gestion des bus des données et des adresses à

un circuit annexe (contrôleur de DMA). Les bus sont en haute

impédance. La ligne BA au niveau haut indique que les bus sont en haute

impédance.

RESET du microprocesseur

Un niveau bas sur la broche d'initialisation RESET entraîne une

réinitialisation complète du circuit

Conséquences :

l'instruction en cours est arrêté

le registre de pagination (DP) est mis à zéro

les interruptions IRQ et FIRQ sont masquées l'interrruption non

masquable NMI est désarmée

Pour être active cette ligne doit être maintenue à un niveau bas durant

un temps suffisamment long (plusieurs cycles d'horloge).

Le P.C. est initialisé avec le contenu des vecteurs d'initialisation qui se

trouvent aux adresses $FFFE et

$FFFF. Ce contenu représente l'adresse du début du programme qui sera

exécuté par le microprocesseur.

Un niveau bas sur la broche HALT provoque l'arrêt du

microprocesseur (mais à la fin de l'exécution de l'instruction en cours).

Il n'y a pas perte des données. (BA = BS = 1)

Dans ce cas :

les demandes d'interruption IRQ et FIRQ sont inhibées

les demandes d'accès direct (DMA) à la mémoire sont autorisée.

les demandes d'interruptions RESET et NMI sont prises en compte mais

leur traitement est différé

5 | P a g e

Fonctionnement des microprocesseurs :

Exemple d’Architecture du microprocesseur : 6809

Architecture interne du 6809 :

Le 6809 possède plusieurs registres utilisés pour la manipulation et le

traitement des données. Ils sont:

➢ 2 accumulateurs de 8 bits A et B transformables en 1

accumulateur de 16 bits, D. Ils sont utilisés pour les instructions

arithmétiques, logiques et de chargement de données 8 bits (ou 16

bits) en mémoire. Ils sont pour cela entièrement identiques.

L'accumulateur D est en fait la concaténation de A et B, le

registre A représentant les poids forts (bits 8 à 15) et B les poids

faibles (bits 0 à 7).

➢ 2 registres d'index X et Y, sur 16 bits. Ils permettent d'adresser

tout l'espace mémoire avec en plus la capacité d'être pré-

décrémenté ou post-incrémenté pour faciliter le traitement de

variables en tables.

➢ 2 registres pointeurs de pile U et S. U (User) est utilisé uniquement

par le programmeur. S (System) par le système pour les

opérations de sauvegarde en cas d'interruption ou de saut à un

sous-programme (Adresse de retour). La pile est un emplacement

ou le microprocesseur sauvegarde le contenu de ses registres

internes pendant un certain temps. Elles opèrent en mode dernier

entré-premier sorti (LIFO : Last In - First Out). Le pointeur de pile

pointe vers la dernière entée effective de la pile.

➢ Un compteur programme PC ( Program Counter), sur 16 bits,

pointe l'adresse mémoire à laquelle le 6809 doit exécuter une

instruction.

➢ Un registre "codes conditions" CC, affichant en permanence l'état

de ces bits. Le contenu du registre d'état est essentiellement

conditionné par l'ALU.

• Le bits C (Carry - BO) est positionné lors d'une opération

arithmétique uniquement. Il est à 1 dans le cas d'une

addition dont le résultat est supérieur à 255 ($FF) ou

lorsque le résultat d'une soustraction (SUB, NEG, CMP,

SBC) est positif. Dans le cas de l'instruction MUL (A

multiplié par B, résultat sur 16 bits dans D), CARRY est

égal au bit B7 de D.

• Le bit V (oVerflow - B1) est le résultat d'un OU EXCLUSIF

entre les retenues arithmétiques de B6 et de B7. Les

opérations logiques de chargements, de stockages et de

transferts positionnent V à 0. Seules les opérations

comme ADD, ADC, SUB, SBC, NEG et CMP

positionnent V à la valeur appropriée.

• Le bit Z (Zéro - B2) est l'indicateur d'un résultat nul. Toutes

les instructions positionnent ce bit.

• Le bit N (NEGATIVE - B3) indique un résultat négatif. Pour

toutes les instructions, N prend la valeur du bit de poids

fort de l'opérande ou de l'accumulateur en mouvement. Il

6

6

7

7

8

8

1

/

8

100%