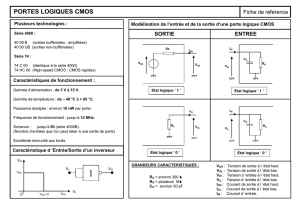

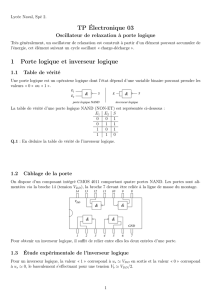

PORTES LOGIQUES CMOS

Rs

RG

VDD VOH

IOH

RSVOL

IOL

CG

VIH

IIN

RG

CG

VIL

IIN

ENTREESORTIE

Modélisation de l’entrée et de la sortie d’une porte logique CMOS

Etat logique ‘ 1 ’ Etat logique ‘ 1 ’

Etat logique ‘ 0 ’ Etat logique ‘ 0 ’

GRANDEURS CARACTERISTIQUES : VOH : Tension de sortie à l ’état haut.

VOL : Tension de sortie à l ’état bas.

VIH : Tension d ’entrée à l ’état haut.

VIL : Tension d ’entrée à l ’état bas.

IOH : Courant de sortie à l ’état haut.

IOL : Courant de sortie à l ’état bas.

IIN : Courant d ’entrée.

RS = environ 300

RG = plusieurs M

CG = environ 50 pF

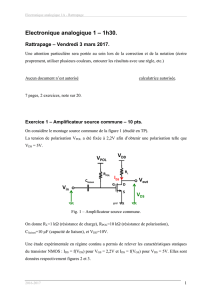

VO

VI

VDD

VDD

VDD / 2

0

Plusieurs technologies :

Série 4000 :

40 00 B (sorties bufférisées : amplifiées)

40 00 UB (sorties non-bufférisées)

Série 74 :

74 C 00 (identique à la série 4000)

74 HC 00 (High-speed CMOS : CMOS rapides)

Caractéristiques de fonctionnement :

Gamme d’alimentation : de 3 V à 15 V.

Gamme de température : de – 40 °C à + 85 °C.

Puissance dissipée : environ 10 nW par porte.

Fréquence de fonctionnement : jusqu’à 12 MHz.

Sortance : jusqu’à 50 (série 4000B).

(Nombre d’entrées que l’on peut relier à une sortie de porte)

Excellente immunité aux bruits.

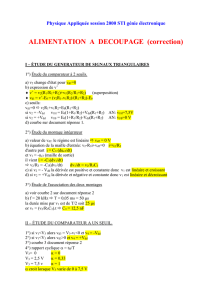

Caractéristique d ’Entrée/Sortie d’un inverseur

PORTES LOGIQUES CMOS Fiche de référence N°7

VIVO

1

/

1

100%