TP SPICE

publicité

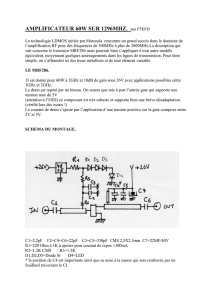

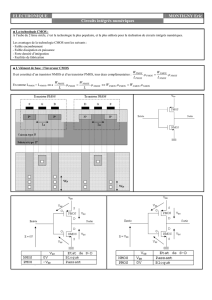

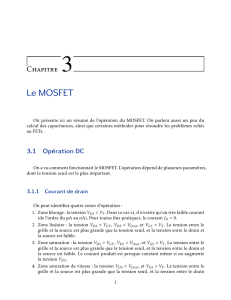

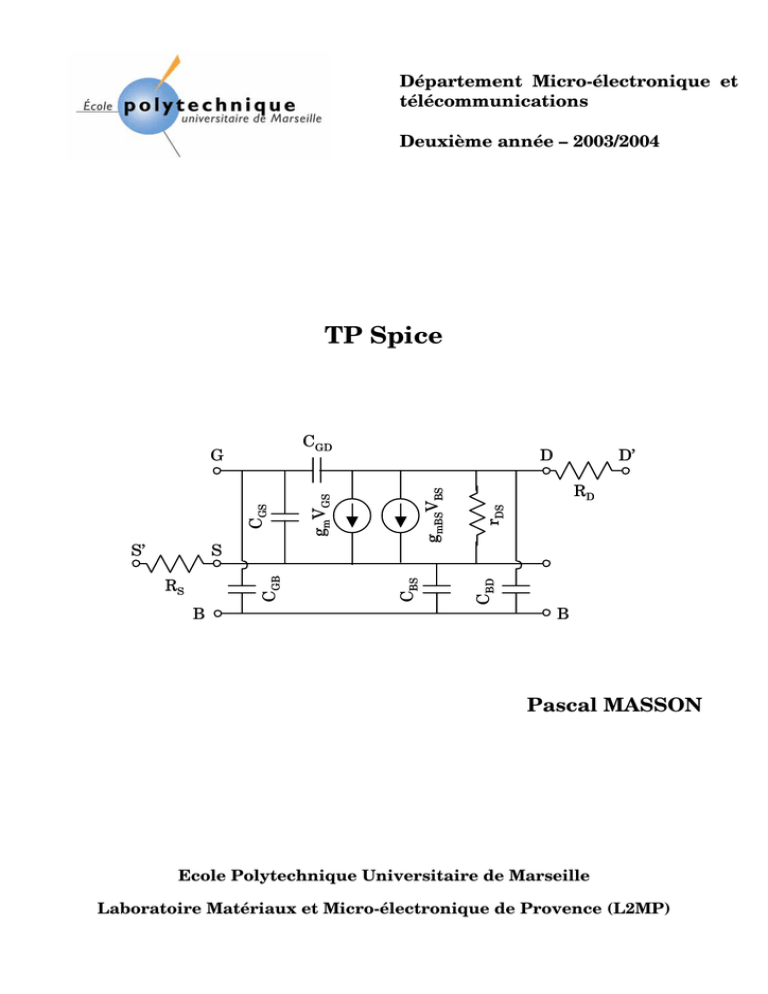

Département Micro-électronique et télécommunications Deuxième année – 2003/2004 TP Spice CGD CGB RS B CBS S S’ D’ rDS RD CBD gmBSVBS D gmVGS CGS G B Pascal MASSON Ecole Polytechnique Universitaire de Marseille Laboratoire Matériaux et Micro-électronique de Provence (L2MP) 2 Table des matières La programmation.............................................................................................. 5 Description du transistor MOS ......................................................................... 9 Prise en main du logiciel ................................................................................. 15 Simulation d’un inverseur CMOS ................................................................... 17 3 4 La programmation I. Les différents niveaux de programmation Il existe quatre méthodes pour décrire un circuit électronique avec un simulateur : 1) Avec le dessin des différents niveaux de masques destinés à la fabrication des composants (TMOS, diodes, résistance…) 2) Avec la netlist qui décrit les composants et les connexions entre eux. 3) Avec le dessin du schéma électrique (placement des composants et connexions entre eux avec des fils). 4) Avec la description d’une fonction. Le logiciel génère seul le schéma électrique avec comme paramètres d’optimisation la surface de silicium utilisée, le temps de propagation… On remarquera que la méthode 1) est très proche du composant puisqu’il décrit sa forme ainsi que la forme des connexions entre les composants. Les méthodes 2) et 3) sont très proches avec une plus grande rapidité d’exécution du circuit pour le point 4). La méthode 4) ne nécessite pas de notions très poussées en électronique ou en physique mais de solides compétences en programmation. Donc en allant de la méthode 1) à la méthode 4) on accélère le temps de réalisation d’un circuit et en allant de la méthode 4) à la méthode 3) on s’approche de la description des composants élémentaires. Lors de la conception d’un circuit intégré, les quatre méthodes de description peuvent être utilisées. Dans le cadre de l’initiation au logiciel SPICE, nous allons utiliser les méthodes 2) et 3). II. La programmation par netlist Dans ce paragraphe, nous décrivons la génération d’un circuit électrique à partir de la netlist. Il est bon de signaler qu’en fonction de la version du logiciel utilisée (plus ou moins récente) les instructions décrites ici peuvent être légèrement différentes. Il est donc préférable d’assimiler ici la philosophie générale de la création d’une netlist. 5 II.1. Structure du programme On peut distinguer les instructions suivantes dans une feuille de programme : - Le titre : la première ligne du programme est obligatoirement prise pour le titre que l’on peut faire précéder par * - Les instructions de description des éléments du circuit : elles doivent être complétées par i) des instructions • model si la description fait appel à des semi-conducteurs, ii) les sousprogrammes éventuellement appelés (pseudo-éléments) - Les commandes : y distinguer les instructions • model, • de simulation, • de sortie - L’instruction de fin de programme : • end II.2. Règles générales d’écriture d’un composant Chaque instruction est terminée par un retour chariot. Une instruction peut être écrit sur plusieurs lignes, les lignes supplémentaires débutant par un + dans le premier emplacement. L’ordre des instructions entre titre et fin de programme est indifférent. Un commentaire commence par un *. Les séparateurs peuvent être le blanc, la virgule, le signe d’égalité et les parenthèses. Une commande commence nécessairement par un point. La description d’un composant doit respecter les règles suivantes : Le nom que l’on donne à un élément commence par une lettre pré-définie : R résistance, C condensateur, L bobine, V source de tension, I source de courant, D diode, M MOSFET… Le nom comporte au maximum 8 caractères alphanumériques ou numériques. Les nœuds. Ce sont des nombres entiers ≥ 0 qui décrivent l’emplacement du composant dans le circuit. La masse est nécessairement 0. Les nombres s’écrivent selon l’échelle usuelle 0.0012, en notation scientifique 1.2E-4, avec un facteur multiplicatif 120U Les facteurs d’échelle (multiplicatifs) sont : T = 1012 (tera), G = 109 (giga), MEG = 106 (mega), K = 103 (kilo), M = 10−3 (milli), U = 10−6 (micro), N = 10−9 (nano), P = 10−12 (pico), F = 10−15 (femto). Les unités sont implicites et correspondent (en générale) au Système International (SI). II.3. Les générateurs de signaux La déclaration d’une source de tension, par exemple, s’écrit : Vxxxxx N+ N− valeur N+ est le nœud supérieur à 0 et N− le nœud inférieur à 0. Le courant est considéré supérieur à 0 si il traverse la source du pôle + vers le pôle −. Si la valeur de la source ne dépend pas du temps (exemple : alimentation), sa valeur peut être précédée du sigle DC. 6 L’analyse AC (alternative) utilise ACMAG (amplitude) et ACPHASE (phase). Une telle source peut, pour l’analyse en régime transitoire, être caractérisée par les cinq fonctions suivantes : Pulse (PULSE), Exponential (EXP), Sinusoidal (SIN), Piece-wise linear (PWL), Single Frequency F-M (SFFM). Dans le cadre de cette initiation au logiciel SPICE, nous n’utiliserons que les fonctions PULSE et SIN : - PULSE : la fonction s’écrit PULSE(V1 V2 TD TR TF PW PER) où les différents termes sont décrits à la figure (II.1). - SIN : La fonction s’écrit SIN(VO VA FREQ TD THETA). De 0 à TD la signal vaut VO et après TD il vaut VO + VA sin[2πFREQ(t − TD)] exp[−(t − TD) THETA]. V TD TR PW TF V2 Figure II.1 V1 t PER Remarque : pour connaître le courant traversant une branche, on peut y placer une source de tension de f.e.m. nulle ce qui ne modifie pas le circuit. II.4. Description du transistor MOS A technologie donnée, les transistors d’un circuit intégré ont certaines caractéristiques identiques telles que le dopage du substrat, l’épaisseur d’isolant, la longueur de diffusion sous la grille… Ces transistors peuvent cependant avoir des dimensions différentes. On distinguera donc le modèle qui décrit la technologie employée et la description des transistors (nom, taille, emplacement…) L’instruction utilisée pour décrire un transistor en particulier dans le circuit est : Mxxxxx ND NG NS NB Mnom <L=valeur> <W=valeur> <AD=valeur> <AS=valeur> +<PD=valeur> <PS=valeur> <NRD=valeur> <NRS=valeur> <OFF> <IC=VDS,VGS,VBS> ND, NG, NS et NB correspondent aux nœuds des quatre entrées du transistor. OFF précise une condition initiale sur le composant pour l’analyse DC. IC=… précise les conditions initiales pour une simulation transitoire. Si les termes entre crochets ne sont pas indiqués, le logiciel leurs donne des valeurs par défaut. La description d’un modèle de transistor (technologie et niveau de modélisation) se fait de la façon suivante : • MODEL Mnom NMOS (ou PMOS) Level=1 (ou plus) <NSUB=valeur> + <LAMBDA=valeur> <GAMMA=valeur> <VTO=valeur> <UO=valeur> 7 II.5. Exemple de netlist Nous présentons ici la netlist qui correspond au circuit de la figure (II.2). * Mosfet à canal n vgs 1 0 DC vds 3 0 DC vfictif 3 2 0 Mn 2 1 0 0 Mmosn L=0.25U W=0.25U • model Mmosn NMOS level=1 tox=4n NSUB=7E17 VT0=0.6 • DC vds 0 2.5 0.05 vgs 0 2.5 0.25 • plot DC I(vfictif) • end On peut aussi préciser les points suivants : vfictif permet d’obtenir le courant de drain avec le bon signe, Dans le terme Mn, n correspond au nom du transistor Dans le terme Mmosn, mosn est le nom que l’on a donné en référence au model utilisé pour ce transistor (• model…) Dans l’analyse DC, la tension vds va varier de 0 à 2.5 V avec un pas de 0.05 V et la tension vgs va varier de 0 à 2 V avec un pas de 0.25 V 2 ID 3 Vfictif 1 Figure II.2. VD VG 0 8 Description du transistor MOS I. Modélisation du transistors MOS Les simulateurs de circuits intégrés sont basés sur des descriptions plus ou moins complexes du comportement électrique des composants. On va ainsi du level1, modélisation très simple, au MM11 qui est une modélisation très proche du comportement physique des composants avec accès aux potentiels internes. On ne s’intéresse, dans ce TP, qu’au modèle de niveau 1 dont nous allons rappeler les équations relatives au fonctionnement du transistor MOS de type N. I.1. La modélisation statique En régime ohmique ou quadratique le courant de drain a pour expression : V I DS = W µ 0C ox VGS − VT − DS (1 + λVDS ) L 2 (I.1) où λ correspond au coefficient de modulation de la longueur du canal, µ0 est la mobilité des porteurs, Cox’ est la capacité de l’isolant par unité de surface et VT représente la tension de seuil : VT = VFB + 2Φ F + 2qN A εSi C ox ' − VBS + 2Φ F (I.2) où NA est le dopage du substrat, VFB est la tension de bandes plates et ΦF le potentiel de volume du substrat donné par : N Φ F = kT ln A q ni (I.3) En régime de saturation c’est-à-dire lorsque la tension de drain devient supérieure à VDSsat = VGS − VT le courant de drain sature (sauf pour λ ≠ 0) et l’équation (I.3) s’écrit dans ce cas : I DS = W µ 0C ox [VGS − VT ]2 (1 + λVDS ) 2L (I.4) En régime bloqué, i.e. pour VGS < VT, on néglige le courant sous le seuil (régime d’inversion faible) ce qui permet d’approximer le courant de drain à 0. I.2. Les petits plus En raison de la diffusion des dopants de la source et du drain sous l’oxyde de grille lors de la fabrication du transistor, la longueur réelle du transistor n’est pas L (longueur de la grille) mais plus petite d’un facteur ∆L qui représente la longueur perdue par cette diffusion. Il en résulte que dans les équations (I.1) et (I.4) le paramètre L doit être remplacé par L − ∆L. On peut aussi, comme le montre la figure (I.1), prendre en compte le courant des diodes de drain et de source (polarisées en inverse) ainsi que la présence des résistances d’accès au canal, 9 RS et RD. On pourra noter que la présence de ces deux résistances réduit la tension réellement appliquée au canal. D’ RD IDS VDS Figure I.1. B RS S’ I.3. La modélisation en petit signal En petit signal, le courant de drain est toujours une fonction des tensions appliquées VGS, VDS et VBS et la variation du courant peut s’écrire : ∂I ∂I ∂I dI DS = DS dVGS + DS dVDS + DS dVBS V V V ∂ ∂ ∂ DS VGS , VBS BS VDS , VGS GS VDS , VBS (I.5) que l’on écrit plus simplement : i D = g m VGS + y DS VDS + g mBS VBS (I.6) D rDS gmVGS gmBSVBS Figure I.2. S Le schéma équivalent du transistor MOS en petit signal est donné à la figure (I.2). Dans ce régime, les diverses capacités parasites du transistor MOS peuvent avoir une influence non négligeable et il est donc nécessaire de les prendre en compte. Comme le montre la figure (I.3), en plus des capacités de désertion des jonctions drain (CBD) et de source (CBS) on compte aussi les capacités grille-source (CGS), grille-drain (CGD) et grille-substrat (CGB). 10 CGD CBS CGB RS B rDS CGS S S’ D’ RD CBD gmBSVBS D gmVGS G Figure I.3. B La capacité CGS est en fait la somme de deux capacités, la première correspond à la capacité de la structure MOS (capacité MOS) et la deuxième à la zone de recouvrement entre la grille et la source (diffusion des dopants sous l’oxyde de grille) de longueur ∆L et de largeur W (c.f. figure (I.4)). On note CGS0 la capacité de recouvrement par unité de longueur (largeur de grille) et la capacité totale, ici en régime de saturation, s’écrit : ε C GS = 2 WL ox + WC GS0 3 t ox (I.7) avec : ε C GSO = ∆L ox t ox (I.8) La capacité CGD est uniquement associée à la diffusion des dopants du drain sous l’isolant de grille et on note CGD0 la capacité de recouvrement par unité de longueur (largeur de grille). Si la structure est parfaitement symétrique, les capacités CGS0 et CGD0 sont identiques. La capacité CGB est due au fait que la grille doit dépasser les zones diffusées de source et de drain. On notera CGB0 la capacité de recouvrement par unité de longueur (longueur de grille). C GB = 2LC GB0 (I.9) CGS0 CGB0 Source CGD0 Drain W L ∆L/2 11 Figure I.4. II. Les notations et paramètres utilisés par SPICE Les conventions d’écriture des modèles utilisés par le logiciel SPICE sont différentes de celles vues en cours (c.f. chapitre I de cette note). Par exemple la tension de seuil hors application d’une tension de substrat est notée VT0, soit avec l’équation (I.3) : VT0 = VFB + 2Φ F + 2qN A εSi C ox ' 2Φ F (II.1) Par ailleurs le dopage du substrat s’écrit NSUB et dans un souci de simplification on pose : GAMMA = 2qNSUBε Si C ox ' (II.2) et : PHI = 2Φ F (II.3) La tension de seuil qui prend en compte l’effet substrat, VTE, s’écrit alors : [ VTE = VT 0 + GAMMA PHI − VBS − PHI ] (II.4) La longueur de diffusion des dopants de source et de drain sous l’isolant de grille est notée LD avec ∆L = 2LD. La mobilité µ0 des porteurs devient UO, l’épaisseur d’isolant tox devient TOX et le paramètre de modulation de la largeur du canal s’écrit LAMBDA = λ. On pose finalement : W β = KP 2 L − 2LD (II.5) avec : KP = UO TOX ε 0 ε ox (II.6) Tous les paramètres (et leurs définitions) utilisés par SPICE sont réunis au tableau (II.1). 12 No. Name 1 2 3 4 5 6 7 8 9 1 11 12 13 LEVEL VT0 KP GAMMA PHI LAMBDA RD RS CBD CBS IS PB CGS0 14 CGD0 15 CGB0 16 17 RSH CJ 18 19 MJ CJSW 20 21 MJSW JS 22 23 24 25 26 TOX NSUB NSS NFS TPG 27 28 29 30 31 XJ LD UO UCRIT UEXP 32 33 34 UTRA VMAX NFFF 35 XQC 36 37 38 KF AF FC 39 40 41 42 DELTA THETA ETA KAPPA Parameter Units Model index − Zero-bias threshold voltage V Transconductance parameter A/V2 Bulk threshold parameter V0.5 Surface potential V Channel-length modulation (MOS1 and 2 only) 1/V Drain ohmic resistance Ohm Source ohmic resistance Ohm Zero-bias B-D junction capacitance F Zero-bias B-S junction capacitance F Bulk junction saturation current A Bulk junction potential V Gate-source overlap capacitance per meter channel F/m width Gate-drain overlap capacitance per meter channel F/m width Gate-bulk overlap capacitance per meter channel F/m length Drain and source diffusion sheet resistance Ohm/sq. Zero-bias bulk junction bottom capacitance per F/m2 square meter of junction area Bulk junction bottom grading coefficient − Zero-bias bulk junction sidewall capacitance per F/m meter of junction perimeter Bulk junction sidewall grading coefficient − Bulk junction saturation current per square meter of A/m2 junction area Oxide thickness m Substrate doping 1/cm3 Surface state density 1/cm2 Fast surface state density 1/cm2 Type of gate material: +1 opposite to substrate, −1 − same as substrate, 0 Al gate Metallurgique junction depth m Lateral diffusion m Surface mobility cm2/V/s Critical field for mobility degradation (MOS2 only) V/cm Critical field exponent in mobility degradation − (MOS2 only) Transverse field coefficient for mobility (MOS2 only) − Maximum drift velocity of carriers m/s Total channel charge (fixed and mobile) coefficient − (MOS2 only) Coefficient of channel charge share attributed to − drain Fliker noise coefficient − Fliker noise exponent − Coefficient for forward-bias depletion capacitance − formula Width effect on threshold voltage (MOS2 and 3) − Mobility modulation (MOS3 only) 1/V Static feedback (MOS3 only) − Saturation field factor (MOS3 only) − Tableau II.1 13 Default Ex. 0 2E−5 0 0.6 0 0 0 0 0 1E−14 0.8 0 1 3.1E−5 0.37 0.65 0.02 1 1 20FF 20FF 1E−15 0.87 4E−11 0 4E−11 0 2E−10 0 0 10 2E−4 0.5 0 0.5 1E−9 0.33 − 1E−8 1E−7 0 0 0 1 1E−7 4E15 1E10 1E10 0 0 600 1E4 0 1U 0.8U 700 1E4 0.1 0 0 1 0.3 5E4 5 0 0.4 0 1 0.5 1E−26 1.2 0 0 0 0.2 1 0.1 1 0.5 14 Prise en main du logiciel Exercice I : Simulation du courant à travers une résistance I.1. Ouvrir une nouvelle feuille de programme avec le logiciel AIM-Spice et réaliser le circuit de la figure (I.1) à l’aide de la netlist en respectant la numérotation des nœuds. I.2. Simuler la courbe IR(t) pour une rampe de tension (Ve ∈ [0, 5V]). Introduire une source de tension nulle dans le circuit pour rendre le courant IR positif. I.3. Simuler la courbe IR(t) pour une tension de type sinusoïdale et de type trapézoïdale. IR 1 Figure I.1. R = 1 KΩ. R Ve 0 Exercice II : Simulation d’un circuit RC II.1. Ouvrir une nouvelle feuille de programme avec le logiciel AIM-Spice et réaliser le circuit de la figure (II.1) à l’aide de la netlist en respectant la numérotation des nœuds. II.2. Visualiser le courant de charge et de décharge du condensateur ainsi que la tension à ses bornes, VC, pour un signal carré (à différentes fréquences). II.3. Visualiser et comparer les tensions VC à la tension Ve (amplitude déphasage) pour un signal sinusoïdal et plusieurs fréquences. Tracer alors la courbe de transfert, VC(f). IR 1 2 R Ve Figure II.1. R = 1 KΩ, C = 1 µF. C 0 15 16 Simulation d’un inverseur CMOS Exercice I : Caractéristiques d’un transistor de type N et P I.1. Ouvrir une nouvelle feuille de programme du simulateur AIM-Spice et réaliser le circuit de la figure (I.1) à l’aide de la netlist en respectant la numérotation des nœuds. I.2. Simuler les courbes ID(VG) et ID(VG) pour VG et VD ∈ [0, 2.5V]. I.3. Faire le même programme et les mêmes simulations avec le logiciel PSpice. 2 3 Vfictif ID Figure I.1. W = 0.25 µm, L = 0.25 µm, tox = 4 nm, µ0 = 300 cm2V−1s−1, Nsub = 7×1017 cm−3, VT = 0.6 V, lambda = 0.1 V−1. 1 VD VG 0 Exercice II : Simulation d’un inverseur NMOS avec résistance II.1. Ouvrir une nouvelle feuille de programme avec le logiciel PSpice et réaliser le circuit de la figure (II.1). II.2. Visualiser la fonction de transfert Vs(Ve) pour différentes résistances R. Commenter vos résultats notamment sur l’allure de la courbe et les inconvénients de ce type d’inverseur. Donner une méthode permettant de déterminer cette courbe (sans le simulateur). VDD = 2.5 V R ID Ve VS Figure II.1. W = 0.25 µm, L = 0.25 µm, tox = 4 nm, µ0 = 300 cm2V−1s−1, Nsub = 7×1017 cm−3, VT = 0.6 V, lambda = 0.1 V−1, R = 1 KΩ. VG 17 Exercice III : Simulation d’un inverseur NMOS avec deux transistors III.1. A la figure (III.1) on donne la photographie d’un inverseur NMOS avec deux transistors que les étudiants de troisième année (option micro-électronique) réalisent au CIME de Grenoble durant le stage technologique. Donner le schéma électrique équivalent de cet inverseur et expliquer la forme particulière du transistor du bas. Figure III.1. Photographie d’un inverseur NMOS à deux transistors. tox = 47 nm, µ0 = 590 cm2V−1s−1, Nsub = 6×1016 cm−3, VT = 1 V, lambda = 0.1 V−1. III.2. Le transistor du haut a pour géométrie W = L = 20 µm. Estimer la géométrie du transistor du bas. Donner alors la fonction de transfert de cet inverseur. Comparer votre résultat avec celui obtenu par mesure. Figure III.2. Mesure de la fonction de transfert de l’inverseur NMOS. Exercice IV : Simulation d’un inverseur CMOS IV.1. Ouvrir une nouvelle feuille de programme et réaliser le circuit de la figure (IV.1). IV.2. Visualiser la fonction de transfert Vs(Ve) et commenter son allure par rapport à celle obtenue à l’exercice précédant. Déterminer par le calcul la géométrie du transistor de type P permettant d’équilibrer l’inverseur. Vérifier votre résultat avec le simulateur. 18 VDD = 2.5 V PMOS Ve VS VG Figure IV.1. W = 0.25 µm, L = 0.25 µm, tox = 4 nm, µ0N = 300 cm2V−1s−1, µ0P = 80 cm2V−1s−1, Nsub = 7×1017 cm−3 VT = 0.6 V, lambda = 0.1 V−1. NMOS Exercice V : L’inverseur CMOS en régime transitoire V.1. Ouvrir une nouvelle feuille de programme et réaliser le circuit de la figure V.1. V.2. Avec une tension Ve de type trapézoïdale mettre en évidence le temps de chargement de la capacité (ou temps de retard). Le temps de montée (ou de descente) du signal d’entrée peut être au minimum de 0.1 ns. VDD = 2.5 V PMOS Ve VS VG C NMOS 19 Figure V.1. W = 0.25 µm, L = 0.25 µm, tox = 4 nm, µ0N = 300 cm2V−1s−1, µ0P = 300 cm2V−1s−1, Nsub = 7×1017 cm−3, VT = 0.6 V, lambda = 0.1 V−1, C = 15 pF.