branchement

1

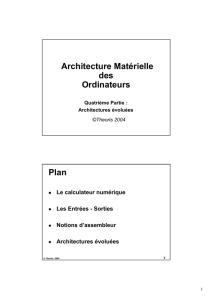

Architecture Mat

Architecture Maté

érielle

rielle

des

des

Ordinateurs

Ordinateurs

©Theoris 2007

Quatrième Partie :

Architectures évoluées

2

© Theoris 2004

Plan

Plan

lLe calculateur numérique

lLes Entrées - Sorties

lNotions d’assembleur

l

lArchitectures

Architectures é

évolu

volué

ées

es

2

Plan quatri

Plan quatriè

ème partie

me partie

u

uIntroduction:

Introduction:

u

uPhilosophie globale

Philosophie globale

u

uRappel historique

Rappel historique

u

uLe march

Le marché

édes processeurs

des processeurs

u

uÉ

Évolution Unit

volution Unité

éCentrale:

Centrale:

u

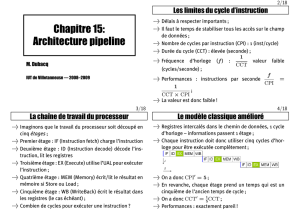

uPipeline,

Pipeline,

u

uPipeline performant:

Pipeline performant:

u

uSuper

Super-

-scalaire

scalaire,

,

u

uEx

Exé

écution sp

cution spé

éculative,

culative,

u

uRenommage

Renommage.

.

u

uTLP

TLP

u

uHi

Hié

érarchie m

rarchie mé

émoire (DRAM, Cache,

moire (DRAM, Cache, …

…),

),

4

© Theoris 2004

Introduction: Philo globale

Introduction: Philo globale

lAugmenter la performance du CPU:

vApproche dirigée par la contrainte de

réalisation jusqu’en 1980 (CISC),

vApproche dirigée par l’étude de la

programmation après 1980, en se basant

sur des jeux de tests (architecture RISC).

lLangage machine est compatible (x86)

Les processeurs d’aujourd’hui sont des

« CRISC » où l’on prend le meilleur des

deux mondes.

3

5

© Theoris 2004

Introduction: RISC vs CISC

Introduction: RISC vs CISC

Compilateur simpleCompilateur complexe Beaucoup de mode d’adressagePeu de mode d’adressage

Toutes les instructions sont

susceptibles d’accéder à la

mémoire

Seules les instructions LOAD et

STORE ont accès à la mémoire

Peu de registresBeaucoup de registres

Décodeur micro-codéDécodeur câblé Format variableFormat fixe

Instructions complexes prenant

plusieurs cycles

Instructions simples ne prenant

qu’un seul cycle

C

CC

Complex

omplexomplex

omplex

I

II

Instruction

nstruction nstruction

nstruction

S

SS

Set

et et

et

C

CC

Computer

omputeromputer

omputer

R

RR

Reduce

educeeduce

educe

I

II

Instruction

nstruction nstruction

nstruction

S

SS

Set

et et

et

C

CC

Computer

omputeromputer

omputer

6

© Theoris 2004

Introduction: historique (1)

Introduction: historique (1)

lÉvolution du CPU pour favoriser

l’exécution d’instructions (famille x86 /

Motorola uniquement):

vAugmentation de la largeur de bits traités:

›4bits en 71 (8086), 32bits en 79 (68000), 64bits

en 92 (AMD Athlon).

vCache: 1975 (68010) quelques octets,

vIntegration des MMU/FPU: 1989 (80486

/68040),

,

vPipeline: 1989 (68040 / 80486), heritage du

RISC

vSuper-scalaire: 1993 (Pentium / 68060)

4

7

© Theoris 2004

Introduction: historique (2)

Introduction: historique (2)

vExécution dé-séquencée: 1995 (Pentium Pro),

vInstructions SIMD: 1993 (Pentium avec le MMX),

vContrôleur mémoire intégré: 2003 (AMD Athlon 64)

lToutes ces améliorations sont possibles

grâce à l’intégration de plus en plus de

transistors sur le CPU (baisse taille gravure)

lAugmentation de la fréquence permet

d’augmenter la performance mécaniquement

lPb récent (2003): le nombre de transistors et

l’augmentation de la fréquence entraînent une

dissipation énergétique qui bruite le signal, et

crée des problèmes de dissipation.

8

© Theoris 2004

Introduction: historique (3)

Introduction: historique (3)

5

9

© Theoris 2004

Introduction: historique (4)

Introduction: historique (4)

10

© Theoris 2004

Introduction: historique (5)

Introduction: historique (5)

lPour pallier au problème de

consommation, on introduit l’exécution

simultanée de programmes

lAugmenter le TLP: Parallélisation

vSMT (Hyper-threading): 2002 ? (Pentium 4)

vCMP (Dual-Core): 2005/2006 (Athlon X2,

Pentium D, Core Duo)

lUne des voies d’avenir des processeurs

est de faire monter le nombre de cœurs

du processeur

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

1

/

52

100%