PIRO_cours_6eme_partie_PUCE_revu_20102016

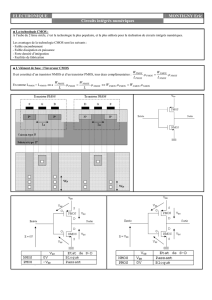

IV. La Jonction.

Jonction PN, diodes et transistors

1. Le premier composant électronique : la diode

A. La jonction

Equivalent à un interrupteur

fermé Equivalent à un interrupteur

ouvert

++

-

-

Tension U “directe”

(dans le bon sens) Tension U “indirecte”

(dans le mauvais sens)

&U < UT

U > UTou

a. Représentation schématique

b. Caractéristiques

C’est une fonction exponentielle de la tension appliquée aux bornes de la diode.

Pour simplifier, si U > UT, le courant passe; sinon, il ne passe pas.

2. Comment fonctionne la diode ? La Jonction PN

Soit 2 « portions » de Si dopées P et dopées N. Si ces 2 portions sont jointes l’une à l’autre

Il y a diffusion des h+(très concentrés à gauche) vers la droite

et diffusion des e-(très concentrés à droite) vers la gauche

Mais les atomes, eux, sont fixes se créent des zones chargées –et +

La réunon de ces deux zones s’appelle la zone de « charges d’espace, ZCE », de largeur W0

Il se crée, dans cette ZCE, un champ électrique, dirigé de + vers -

a. La jonction PN en court-circuit :

E

W0(largeur de la ZCE)

E (champ électrique)

+

-

?

Que se passe-t-il, en terme d’énergie, dans la ZCE ?

EFp

EFn

EFi EFi

BCBC

BV

BV

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

1

/

37

100%