texte

1

MASTER 2

Nanodispositifs et nanotechnologies

Composants et antennes pour les télécommunications

Univ. Paris Sud – ENS Cachan – ECP

2011-2012

Examen du 21 novembre 2011

Durée : 3h. Les documents ne sont pas autorisés et les calculatrices non nécessaires. Ce texte comporte

trois parties indépendantes les une des autres.

I. Masses de densité d'états et densité d’électrons et de trous

On étudie un cristal semiconducteur. La concentration en électrons (respectivement en trous) d’un

semiconducteur homogène à l’équilibre thermodynamique peut être évaluée à partir d’une part, du

nombre d’états nC(E) (resp. nV(E)) en énergie susceptibles d’être occupés par les électrons (resp. par les

trous) d’énergie E, et d’autre part, de la probabilité fn(E) (resp. fp(E)) de chacun de ces états d’être occupé

ou non, par des électrons (resp. trous). On définit les niveaux d'énergie suivants : EC, le minimum de la

bande de conduction, EV le maximum de la bande de valence, EF le niveau de Fermi.

On rappelle les expressions suivantes :

- Densité d'états dans la bande de conduction : nC(E) = 8 2

3/2

*1/2

2()

eC

mEE

h

.

- Densité d'états dans la bande de valence: nV(E) = 8 2

3/2

*1/2

2()

tV

mEE

h

.

- Fonction de distribution des électrons :

1

()

1 exp

nF

B

fE EE

kT

On donne :

02

x

xe dx

1- Quelle est la densité d'états dans l'espace des vecteurs d'onde ? En déduire l'expression de nC(E).

2- Démontrer que pour un semiconducteur à vallée sphérique au niveau de la bande de conduction, la

densité d'électrons dans la bande de conduction d'un semi-conducteur non dégénéré peut se mettre sous la

forme : n = NC

exp

CF

B

EE

kT

. On précisera soigneusement comment sont utilisées les hypothèses

énoncées.

3- Expliquer en quoi consiste le dopage d’un semiconducteur. Vous envisagerez le cas d’un dopage de

type "accepteur" et de type "donneur", en précisant le sens de ces notions. Déterminer les domaines de

dopage accepteur (en concentration NA) et donneur (en concentration ND) pour lesquelles les expressions

établies aux questions 2 et 3 sont valables ; on supposera pour cela qu’à la température considérée chaque

atome dopant libère un électron (ou un trou) libre.

4- Indiquer comment le Si peut être soit un dopant accepteur, soit un dopant donneur dans GaAs.

On applique sur Si dopé N une contrainte uniaxiale d'amplitude K et selon l'axe x. La variation en

énergie du minimum des ellipsoïdes de conduction dans le silicium contraint est donnée

par :

2

ee

eD

3

2

Eyyzz

xx//

si le grand axe de l'ellipsoïde est suivant la direction de la contrainte et

2

par

2

ee

e

3

D

Eyyzz

xx

si le grand axe est suivant les directions perpendiculaires à la

contrainte, où le potentiel de déformation uniaxiale est D = 9 eV. On indique la loi de Hooke :

zz11yy12xx12

zz12yy11xx12

zz12yy12xx11

eCeCeC0

eCeCeC0

eCeCeCK

soit

GPa

12111211

12

zzyy

GPa

12111211

1211

xx

K002,0K

CCC2C C

ee

K008,0K

CCC2C CC

e

5- Représenter schématiquement les surfaces iso-énergies dans les vallées de la bande de

conduction de Si non contraint.

6- Démontrer que dans Si non contraint la masse de densité d'états associée aux vallées est donnée

par

0

3/2

2/12/12/1* 06,16 mmmmm ttle

où ml est la masse longitudinale (0,92 m0), mt la masse

transverse (0,19 m0) et m0 la masse de l'électron dans le vide.

7- Comment se déplacent les minima des 6 ellipsoïdes en fonction de la contrainte ? On notera

respectivement ∆Ex, ∆Ey et ∆Ez les décalages.

8- Le matériau étant toujours contraint, donner l'expression qui permet de calculer la nouvelle densité

volumique d'électrons et en déduire leur masse effective. On posera pour cela

Tk

K

CC D

Tk

EE

B1211B

z,yx

.

II. Jonction PN et transistor bipolaire

On considère une jonction entre un semiconducteur de type N et un semiconducteur de type P. Dans

tout le problème, on fera l’hypothèse de complète déplétion. Les notations relatives aux deux zones sont

reportées sur le tableau ci-dessous. On considère que les deux zones de la jonction PN (zone P pour x < 0,

N sinon) sont constituées du même semiconducteur.

Dopage

Epaisseur zone

Epaisseur ZCE

Coefficient diffusion minoritaires

Zone N

ND

Xn

xn

Dpn

Zone P

NA

Xp

xp

Dnp

On a de plus :

dx

dn

qDEqnJnnn

et

dx

dp

qDEqpJppp

x

J

q

UG

t

nn

nn

1

et

x

J

q

UG

t

pp

pp

1

D’après la statistique de Shockley-Read-Hall, la vitesse de génération-recombinaison thermique

s’exprime sous la forme :

)np()nn( npn

UG ii

2

i

.

1- Expliquer ce qui se passe à la jonction métallurgique entre la zone N et la zone P sous tension nulle

appliquée. On définira la zone de charge d’espace et le potentiel de diffusion D.

2- Calculer D puis l'épaisseur de la zone de charge d'espace WZCE en fonction des paramètres

nécessaires.

3

3- On polarise la jonction en direct sous une tension VF. Préciser le sens de cette polarisation. Tracer

l'allure du potentiel électrostatique en le comparant au cas de la question 1. Expliquer quels sont les

phénomènes qui peuvent conduire à un courant.

4- Rappeler l'hypothèse de faible injection. En se plaçant dans ce cas, démontrer que G-U s'exprime

sous la forme –n/ (resp. –p/) dans une zone de quasi neutralité de type P (resp. N) où n (resp. p)

représente l’excès de concentrations en électrons (resp. trous) minoritaires par rapport à l’équilibre

thermodynamique.

5- Etablir alors l’équation permettant de calculer la densité d’électrons injectés dans la zone P. On

supposera

pn XD

dans la zone P. Quel phénomène physique peut être négligé avec cette dernière

hypothèse ?

6- En définissant les conditions aux limites, déterminer l’expression de cette densité d’électrons. En

déduire le courant d’électrons.

7- Toujours dans l’hypothèse des faibles injections, donner l'expression du courant dû aux trous

injectés dans la zone N. On étudiera les deux cas suivants :

np XD

et

np XD

.

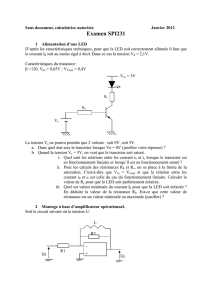

Sur une plaquette de silicium de type N dopé ND on a créé deux caissons P+ dopés NA comme indiqué

sur la figure suivante. Seule la moitié de la largeur Z des caissons P+ est représentée (largeur Z

globalement). La jonction base-émetteur est polarisée en direct et la jonction base-collecteur en inverse

sous une tension inférieure à celle de claquage.

e=2µm

L=3µm

Z/2=10µm

Wb=5µm

L=3µm

y

x

z

Figure n°1 : Transistor PNP latéral.

8- Préciser comment doit-on brancher des générateurs de tension continue dans un schéma base

commune pour assurer le fonctionnement précédant. Indiquer quels sont les courants de diffusion qui

circulent dans le transistor.

9- Etablir l'expression du courant de trous à l'émetteur sachant que dans la base

bp WD

mais qie

la longueur de diffusions des trous est très faible devant les dimensions de la zone N dans les directions y

et z.

10- En négligeant les courants d'électrons, établir les expressions des gains en courants en base

commune aF et en émetteur commun bF.

4

III. Transistor MOSFET (Metal Oxide Semiconductor Field Effect Transistor)

On considère un transistor MOSFET à canal N à grille longue et de type "normally off". On note Cox

la capacité d'oxyde par unité de surface, LG la longueur de grille, W la largeur de grille, µn la mobilité des

électrons, VGS, VDS, VBS et (x) les tensions respectives entre la grille et la source, le drain et la source,

le substrat et la source et le canal et la source. On admettra que la densité surfacique de charges dans le

canal QI(x) est donnée par

QI(x) = –Cox (VGS – VT – (x))

où VT est une constante indépendante des tensions appliquées.

1- Représenter le schéma en coupe d'un tel transistor, réalisé sur substrat P. On précisera la définition

de la source et du drain ainsi que le sens du courant de drain ID.

2- Décrire qualitativement ce qui se passe dans le substrat sous la grille quand VGS varie alors que

VDS = VBS = 0 V. On précisera en particulier ce qu'est le régime de bande plate (ou "flat band") ainsi que

la signification physique du paramètre VT de l'équation précédente.

3- Etablir, en précisant les approximations utilisées, l'équation donnant le courant dans le canal ID

quand le canal est constitué de la source jusqu'au drain.

4- Expliquer pourquoi ID sature par rapport à VDS quand VDS > VGS – VT.

5- Déduire du résultat de la question 3 l'expression du courant de saturation IDsat.

6- Pourquoi est-il intéressant de réduire LG pour accroître la rapidité d'un circuit logique CMOS

(Complementary Metal Oxide Semiconductor) ?

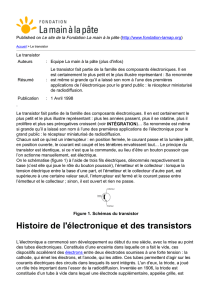

Les images suivantes présentent un schéma de principe et une vue en microscopie électronique à

transmission d'une architecture de transistor à "multi-canaux" réalisée récemment dans le cadre d'une

thèse STMicroelectronics/CEA-LETI. Cette structure est définie grâce à la gravure sélective de couche de

SiGe dans une multicouche Si/SiGe/Si/SiGe/Si/SiGe qui permet de libérer les volumes permettant de

réaliser les 3 grilles (gates) étagées, reliées par ailleurs à la même électrode. Le transistor repose sur un

substrat de type SOI pour Silicon On Insulator. BOX est un sigle pour "buried oxide", couche d'oxyde

enterrée qui sépare la zone active du transistor du reste du substrat (bulk). Les dopages de source et drain

ne sont pas indiqués sur le schéma.

Figrue n°2 : Transistor multi-canaux, schéma et image TEM reproduits de l'article de E. Bernard, T. Ernst, B. Guillaumot,

N. Vulliet, P. Coronel, T. Skotnicki, S. Deleonibus, O. Faynot, "Multi-Channel Field-Effect Transistor (MCFET)-Part I:

Electrical Performance and Current Gain Analysis," IEEE Transactions on Electron Devices, vol. 56, pp. 1243-1251, 2009.

7- Expliquer comment une fuite de courant peut s'établir entre source et drain dans l'état off d'un

transistor à effet de champ de type MOSFET à architecture plus "classique" sur substrat massif. Quel est

l'inconvénient de ce courant Ioff par rapport à des applications en logique CMOS ?

5

8- Vis-à-vis du courant off, quel peut-être l'intérêt de réaliser un MOSFET sur un substrat SOI à film

actif ultra-mince comme sur la Fig. 2 ?

9- Quel est l'intérêt d'utiliser un oxyde d'hafnium HfO2 au lieu de la silice SiO2 pour séparer le Si des

grilles TiN/poly-Si ? Quel(s) inconvénient(s) cela peut-il induire ?

10- Qu'est-ce que le poly-Si et pourquoi est-il souvent utilisé comme matériau de grille ?

11- Quel peut être l'intérêt vis-à-vis des effets de canal court de la prise en sandwich des canaux

ultra-minces 1 et 2 d'une part, 3 et 4 d'autre part entre deux grilles (DG) ?

Les caractéristiques courant-tension de transistors à multi-canaux de type PMOS et NMOS sont

indiquées ci-dessous. SS est la pente sous le seuil (subthreshold slope), le DIBL (Drain induced barrier

lowering) est associé à la variation de tension de seuil VT quand VDS varie de 50 mV à 1,2 V (tension

d'alimentation VDD des transistors) normalisée par 1,15 V. CET (capacitance equivalent thickness) est

une épaisseur de SiO2 équivalente déduite de la mesure des capacités MOS dans la structure.

Figure n°3 : Caractéristiques courant-tension du transistor à multi-canaux de la figure 2.

12- Quel effet de canal court d'abaissement de barrière est caractérisé par le DIBL ? Que penser des

valeurs reportées ici ?

13- Pourquoi le courant Ion dans le PMOS est-il plus faible que dans le NMOS ?

14- Que penser des rapports Ion/Ioff obtenus ?

1

/

5

100%