Contrôle continu du 28 novembre 2008

Faculté des Sciences de Montpellier, UM2

Yves Bertrand 30/11/08

Année universitaire : 2008/2009

Diplôme : Master EEA

Epreuve : Conception des circuits intégrés CMOS analogiques

Contrôle continu du 28 novembre 2008

Durée : 1h30

Contrôle continu du 28 novembre 2008

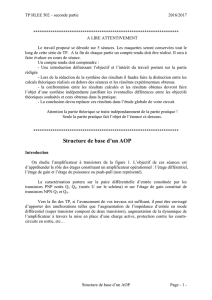

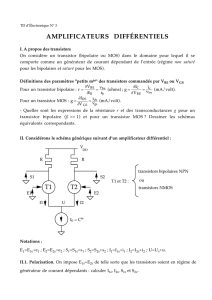

Soit l'amplificateur opérationnel CMOS dont le schéma est donné ci-dessous.

M3

VDD

M1M2

M7

VSS

M4

M5

M6

M9

66/10

27/10

53/10

133/10

10/66

293/10

M10

66/10

59/1059/10

In1In2

Out

A

B C Q

P

Les dimensions des transistors (W/L) sont directement indiquées sur le schéma.

Constantes physiques et paramètres de fabrication:

Permittivité du vide : ε

0

= 8,85.10

-12

F.m

-1

Constante diélectrique du dioxyde de silicium : ε

r

(SiO

2

) = 3,9

Mobilité des électrons dans le silicium à 300K : µ

n

= 670 cm

2

.V

-1

.s

-1

Mobilité des trous dans le silicium à 300K : µ

p

= 268 cm

2

.V

-1

.s

-1

Paramètres de fabrication : t

ox

= 38,5nm ; λ= 0,02V

-1

; V

tn

= 1,2V et V

tp

= -1V

Tensions d'alimentation : V

DD

= -V

SS

= 5V

1 / Etude générale (4 points)

a ) Combien y a-t-il d'étages dans cet amplificateur ? Donner la liste des transistors pour chacun de ces étages en

expliquant la fonction de ces transistors ?

b ) Déterminer par une analyse qualitative les entrées inverseuse (+) et non inverseuse (-) de l'amplificateur

complet.

c ) Démontrer que le facteur de transconductance des transistors NMOS est : k

pn

=60µA.V

-2

. En déduire facteur

de transconductance k

pp

des transistors PMOS.

2 / Etude de la polarisation (8 points)

a ) Quelle est la condition nécessaire à respecter sur le potentiel V(P) pour que le circuit puisse fonctionner ?

Quel est alors le régime de fonctionnement du transistor M

9

. Justifier.

b ) A quelle valeur particulière est égale la somme des V

GS

des transistors M

9

et M

10

?

En déduire la valeur du courant I

D10

, puis de celle des courants I

D1

, I

D2

, …, I

D9

dans tous les autres transistors

(Remarque : il n'y a pas de transistor M

8

dans le montage).

3 / Etude du gain différentiel du premier étage (5 points)

a ) Donner le schéma dynamique petit signal du 1° étage du circuit, dans le cas d'une attaque purement

différentielle : v

In1

= +v

d

/2 et v

In2

= - v

d

/2.

b ) Déterminer le gain différentiel de cet étage A

V1

=v

C

/v

d

.

Expression littérale complète (sans approximation)

Expression approximée (on doit retrouver un résultat connu)

Valeur numérique.

4 / Etude du gain différentiel du circuit complet (3 points)

a ) Donner le schéma dynamique petit signal du l'étage de sortie.

b ) Déterminer le gain de cet étage : A

V2

=v

Q

/v

C

: valeur littérale, puis valeur numérique.

c ) Déterminer le gain différentiel total de l'AOP complet : A

V

=v

out

/v

d

.

1

/

1

100%