Electronique De Commutation

Electronique de commutation par A. Oumnad 1

Electronique

De

Commutation

A. Oumnad

Electronique de commutation par A. Oumnad 2

SOMMAIRE

I Composants en commutation .........................................................................................3

I.1 Rappels ........................................................................................................................3

I.1.1 Diviseur de tension ............................................................................................3

I.1.2 Diviseur de courant............................................................................................3

I.2 Cellule RC ....................................................................................................................3

I.2.1 RC Passe bas........................................................................................................3

I.2.2

RC passe haut......................................................................................................4

I.3 Caractéristiques d'un commutateur.....................................................................6

I.4 La diode en commutation.........................................................................................8

I.4.1 Comportement dynamique d’une diode ..........................................................9

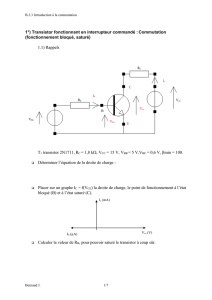

I.5 Transistor bipolaire en commutation ................................................................. 10

I.5.1 Temps de commutation ................................................................................... 12

I.5.2 Commande dynamique d'un transistor de commutation .......................... 13

I.5.3 Application : Multivibrateur Astable........................................................... 15

I.6 Transistor MOS à enrichissement ..................................................................... 17

I.6.1 Commutateur analogique (porte analogique) .............................................. 17

I.7 Amplificateur opérationnel................................................................................... 18

I.7.1 Fonctionnement en boucle ouverte, COMPARATEUR.............................. 18

I.7.2 Fonctionnement en comparateur à seuil unique ........................................ 19

I.7.3 Fonctionnement en contre réaction positive ............................................. 19

I.7.4 Application : Multivibrateur astable........................................................... 22

I.8 Le Timer 555 .......................................................................................................... 23

I.8.1 Utilisation en monostable.............................................................................. 23

I.8.2 Fonctionnement en ASTABLE ...................................................................... 25

II ANNEXE : Transistor à effet de champs à jonction........................................ 27

II.1.1 I-5.3 Paramètres dynamiques d'un JFET .............................................. 29

II.1.2 I-5.1 MOS à enrichissement ............................................................... II-33

II.1.3 I-5.2 MOS à déplétion ......................................................................... II-34

III famille de circuits logiques.......................................................................... III-36

Les familles logiques principales .......................................................................... III-36

Model fonctionnel d'une porte logique ............................................................... III-36

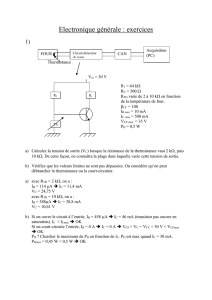

IV TRAVAUX DIRIGES ..........................................................................................IV-39

Electronique de commutation par A. Oumnad 3

I COMPOSANTS EN COMMUTATION

I.1 Rappels

I.1.1 Diviseur de tension

V1

V =

V3

R3

R1 ++

R2

V2

++

R1

1

R2

1

R3

1

V1

V = R1+R2

R2 V1 V = R1+R2

R2 V1 + R1+R2

R1 V2

R1

R2

V

V2

V1

R1

R2

V

V2

V1

R1

R2

V

V3

R3

I

.1.2 Diviseur de courant

21

21

21

1

2

21

12

21

2

1

RR VV

I

RRR

I

RR VV

I

RRR

I

+

−

+

+

=

+

−

+

+

=

I

RRR

I

I

RRR

I

21

1

2

21

2

1

+

=

+

=

I

I2

I1

R2

R

1

V1 V2

I

I2

I1

R2

R1

I.2 Cellule RC

I.2.1 RC Passe bas

I.2.1.1 Réponse à un échelon

L'équation de toute charge ou décharge d'une

capacité peut s'écrire sous la forme suivante.

()

τ

t

eVV −

∞−0

VtV ∞−=)(

Dans notre cas V∞=E, Vo=0, τ=RC : Constante

de temps.

Vs(t)=E(1-e-t/τ)

τ est le temps que met le signal Vs pour

atteindre 63% de sa valeur finale,

t=0

Vs

t

E

t=0

Ve

t

E

Vs

Ve R

C

Fig. I-1 : Réponse à un échelon d'une cellule RC

passe bas

en effet : Vs(τ)=E(1-e-τ/τ)=E(1-1/e)=0,63E

Ne pas confondre avec le temps de montée Tr

(

Rising Time)

qui correspond au temps que met

le signal pour passer 0,1E à 0,9E.

Electronique de commutation par A. Oumnad 4

on retiendra la règle suivante :

Plus RC=

τ

faible ⇒ Plus la réponse est rapide

I.2.1.2 Réponse à un rectangle

• t ∈ [to,t1[ ⇒ Charge de la capacité

to

Vs

E

to

Ve

t

E

t1

t

t1

Vo

T

Fig. I-2 : Réponse à un rectangle d'une

cellule RC passe bas

Vs(t)=E(1-e-t/τ) (to origine du temps)

• t > t1 ⇒ Décharge de la capacité Vs = Vo e-t/τ

(t1 Origine du temps ) Vo = E(1 - e-T/τ )

On retiendra que :

plus

τ

= RC est faible ⇒ plus le signal de

sortie ressemble au signal d'entrée

I.2.2

RC passe haut

Vs

t

E

Ve

t

E

Vc

R

C

to

to

Ve Vs

Vc

Fig. I-3 : Réponse à un échelon d'une cellule RC

passe haut

I.2.2.1 réponse à un échelon

On entendra souvent :

La capacité transmet

les fronts de tension

, qu'est ce que cela

voudrait il dire? Pour le savoir, on va faire

l'analyse de ce qui se passe après l'instant to

sachant les choses suivantes :

• Ve = Vc + Vs

• Au repos (t < to), aucun courant ne circule

dans le circuit RC.

• Une capacité ne peut pas se charger

instantanément.

On peut donc affirmer les résultats suivants :

• à t = to - ε Ve=0, VR = Vs = 0 ⇒ Vc = 0,

(capacité déchargée).

• à t = to + ε Ve = E, Vc = 0, ⇒ Vs = Vc - Ve =

E

Electronique de commutation par A. Oumnad 5

Donc on voit bien que le front de tension apparu à l'entrée du montage se

retrouve à la sortie. Il est évident que les choses ne restent pas ainsi, (

On a dit

que la capacité ne se chargeait pas instantanément, mais on n'a pas dit qu'elle

ne se chargera jamais)

Donc la capacité se charge avec la constante de temps

RC.

Vc(t) = E(1 - e-t/τ )

Vs(t) = E - Vc(t) = Ee-t/τ

On peut essayer d'aborder le phénomène de transmission de fronts de tension

sur un aspect différent, en effet, l'Impédance (module) d'une capacité est :

Zc CC

==

11

2f

ω

π

Donc cette impédance est quasiment nulle pour les hautes fréquences, or

justement un front de tension équivaut à une fréquence très élevée (V

ariation

très rapide

) La capacité se comportera donc comme un court-circuit (

bout de fil

en cuivre

) pour les fronts de tension qui lui sont appliqués. C'est l'approche qui

consiste à faire l'étude de la réponse harmonique d'un filtre passe haut. le front

de tension correspond à un harmonique très élevé donc bien supérieur à la

fréquence de coupure du filtre, il est donc transmis avec un gain = 1.

I.2.2.2 Réponse à un rectangle

to

Vs

t

E

to

Ve

t

E

t1

V1

V2

Vs Vc

V3

T

Fig. I-4 : Réponse à un rectangle d'une cellule RC passe

haut

• t ∈ [ to , t1[ ⇒ La capacité

transmet le front puis se charge vers

E avec la constante de temps RC.

⎟

⎠

⎞

⎜

⎝

⎛−= −

τ

t

Ce1EV , VV

V

Sec

=−=Ee

t

−τ

• t = t1 ⇒ De nouveaux la capacité

transmet le font (descendant cette

fois) vers la sortie qui passe de V1 = à

V3 . Vc = V2 et

τ

T

1Ee−

=V.

⎟

⎠

⎞

⎜

⎝

⎛−=−= −1eEEVV T

13

τ

, ⎟

⎠

⎞

⎜

⎝

⎛−= −

τ

T

2e1EV

• t > t1 ⇒ Décharge de la capacité vers

zéro.

τ

t

2C VV −

= ,

ττ

t

T

SCSSCe e1eEVVV0VVV −− ⎟

⎠

⎞

⎜

⎝

⎛−=⇒−=⇒=+=

On peut conclure que :

τ grand ⇒ La sortie est quasi rectangulaire .

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

1

/

42

100%