Cours 6 - Université Laval

GIF-1001

Cours 6, p.1

Etienne Tremblay

Ordinateurs, Structure

et Applications

GIF-1001

Université Laval, Hiver 2012

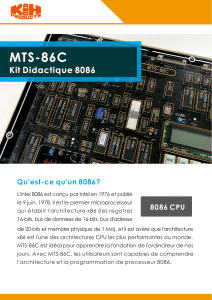

Cours 6, le 8086

GIF-1001

Cours 6, p.2

Introduction

• Un objectif du cours d’OSA est d’apprendre la programmation en

assembleur.

• De nos jours, il est très très rare de programmer en assembleur: très peu de

personnes programment en assembleur et ceux qui le font, le font

habituellement très peu souvent. Cependant, il est important de bien

comprendre les instructions et l’exécution d’instructions afin de bien

comprendre comment fonctionne un ordinateur. Comme les instructions sont

intimement reliées au code assembleur, le langage assembleur est présenté

dans le cours d’OSA.

• Un pré requis quasi-incontournable de la programmation en assembleur est

de bien connaître le microprocesseur qui exécutera le programme. Le

langage assembleur est très près du langage machine.

• Pour cette raison et pour faire un lien avec le cours précédent sur

l’architecture des microprocesseurs, le 8086 sera présenté brièvement en

classe.

GIF-1001

Cours 6, p.3

Le 8086

(1)

Tiré de: i8086_microprocessor.pdf

GIF-1001

Cours 6, p.4

Le 8086 (2)

• Le 8086 a des registres de 16 bits et peut adresser 1Mo de mémoire (20 bits

d’adresse). La mémoire est externe au CPU.

• Le 8086 gère 4 segments de 64Ko.

• Le 8086 a une architecture CISC. Chaque instruction du 8086 a une

longueur qui lui est propre.

• L’horloge du 8086 peut être 5, 8 ou 10MHz. Un cycle du CPU vaut 6 coups

d’horloge. Une instruction de CPU peut habituellement être exécutée par

cycle (En fonction de l’instruction).

• Le 8086 a 40broches. 20 broches servent de bus d’adresses et 16 broches

servent de bus de données. Afin de minimiser le nombre de broches, les 16

broches de données sont aussi des lignes d’adresse. Lors d’une opération

d’écriture ou de le lecture de la mémoire, les 16 broches communes

(adresses et données) sont tour à tour des adresses, puis des données. Les

autres broches du 8086 servent au contrôle des bus (Interruptions, Read,

Write, I/Os versus mémoire, etc.) ou à l’opération du 8086 (alimentation,

horloge, reset).

• Le 8086 est divisé en plusieurs bloc fonctionnels qu’on retrouve dans un

CPU moderne: le Bus Interface Unit, des registres (il n’a pas de registres

pour les fractions), un ALU, un buffer de 6byte pour 1 instruction et une unité

de contrôle et d’exécution des instructions.

GIF-1001

Cours 6, p.5

Le 8086 (3) Tiré de: i8086_microprocessor.pdf

6

6

7

7

1

/

7

100%