doc

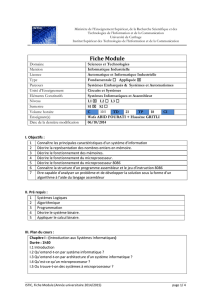

Cours 5 : Introduction aux microprocesseurs

Q5.1 : Qu’est-ce qu’un ALU?

Un circuit électronique qui effectue des opérations mathématiques et logiques.

Q5.2 : Qu’est-ce que le Control Central Unit d’un microprocesseur?

C’est la partie du microprocesseur qui lit, décode et exécute les instructions.

Q5.3: Lorsque le microprocesseur lit une instruction, où la met-il avant de la décoder?

Le microprocesseur a un registre ou un tampon qui contient la ou les dernières instructions lues en mémoire.

Q5.4 : Combien de coups d’horloges sont requis pour lire et exécuter une instruction?

Il n’y a pas de réponse unique à cette question : ça dépend du microprocesseur, de la mémoire, de la vitesse

d’horloge, de l’instruction et de plusieurs autres facteurs (caches, bus et accès au bus, architecture du

microprocesseur, jeu d’instructions…). Habituellement, les microprocesseurs modernes (disons depuis 2005)

exécutent plusieurs instructions par coup d’horloge (une moyenne entre 2 et 4, en fonction du microprocesseur et

des instructions à exécuter).

Q5.5 : De combien est incrémenté automatiquement PC entre chaque instruction?

PC est incrémenté de la taille de l’instruction exécutée, à moins que les instructions ne disent de faire autrement.

Q5.6 : À quoi sert la ligne de contrôle LOAD/COUNT pour le CPU en exemple dans le

cours 5?

Déterminer s’il faut charger la prochaine série de micro-instructions qui sera à exécuter ou s’il faut continuer la

série de micro-instructions actuelle.

Q5.7 : À quoi sert l’entrée 0 pour le MUX A et le MUX B pour le CPU en exemple dans le

cours 5?

Permettre de mettre un registre ou l’accumulateur à zéro facilement, ou rendre nulle l’une des entrées de l’ALU

pour faire des affectations.

Q5.8 : Pour le CPU en exemple dans le cours 5, quel est la valeur des lignes de contrôle

pour la sous-instruction MDR+A->A? Inspirez-vous de l’acétate « Microprogramme pour

addition (Annexe) » afin de répondre.

Même réponse que dans l’acétate, sauf pour un seul champs de l’u-instruction 124 : MUX_B SEL doit être ACC.

Q5.9 : Pourquoi a-t-on besoin du registre MAR?

Il faut un buffer où mettre la valeur des lignes d’adresses voulues.

Q5.10 : Quel matériel pourrait être utilisé afin de concevoir un registre?

Bascules SRs, bascules D, autres flip-flops…

Q5.11 : Donnez quatre différences entre une architecture RISC et une architecture CISC.

Longueur des instructions

Taille des programmes

Nombre de registres

Facilité de traitement des instructions

Q5.12 : Donnez trois conséquences d’utiliser des instructions ayant toujours la même

longueur?

Pipeline plus facile a implémenté

Program counteur plus facile a géré

Moins d’instructions possibles

Q5.13 : Qu’est-ce qu’un pipeline?

Une série de composantes matérielles indépendantes exécutant chacune une partie d’une instruction. Chaque

composante peut travailler sur une instruction différente.

Q5.14 : Dites si les énoncés suivant sont vrai ou faux. Justifier dans tous les cas :

A) Un pipeline permet toujours de compléter une instruction par coup d’horloge

Faux. Il peut y avoir des dépendances entre les instructions. Il y a aussi des instructions de saut, des

branchements, etc.

B) Un ordinateur super scalaire sera assurément plus performant qu’un ordinateur

scalaire.

Faux.

C) Un pipeline ayant une profondeur de 6 exécute 6 instructions à la fois et l’exécution

de chaque instruction est divisée en 6 parties.

Vrai

Q5.15 : Nommez cinq composantes d’un CPU moderne.

CCU, ALU, Registres, unité de gestion des bus externes, unité de traitement des sauts pour la pipeline, etc.

Q5.16 : Qu’est-ce qu’une micro instruction? Quel est l’avantage d’utiliser des micro-

instructions par rapport à concevoir un micro processeur avec une logique câblée

(hardwired, c’est-à-dire où chaque instruction est exécutée par une séquence d’action dans

du matériel qui lui est propre).

Une micro instruction est une étape d’une instruction. Chaque instruction est exécutée avec une séquence de

micro instructions. Comme des instructions différentes ont souvent plusieurs parties commune, utiliser des

microprogrammes permet de réduire la quantité et la complexité du matériel nécessaire à l’exécution des

instructions.

Q5.17 : Lors de la lecture et de l’exécution d’une instruction comme LOAD R0, MaVar

(lire MaVar en mémoire et mettre la valeur lue dans le registre R0), le microprocesseur met

des adresses sur le bus d’adresse. Dites combien d’adresses seront mises sur le bus

d’adresse et quel registre du microprocesseur fournira l’adresse.

Deux adresses seront mises sur le bus d’adresse :

- L’adresse de l’instruction LOAD, fournie par le compteur de programme (registre PC)

- L’adresse de la variable MaVar, fournie par l’instruction elle-même (registre IR)

Q5.18 : L’annexe du cours 5 présente un microprocesseur rudimentaire. Expliquez quelles

seraient les sous-instructions nécessaires afin de lire et d’exécuter l’instruction LOAD R0,

MaVar (lire MaVar en mémoire et mettre la valeur lue dans le registre R0), puis lire et

exécuter l’instruction ADD R0, R0, R0 (additionne R0 = R0 + R0), pour ce

microprocesseur rudimentaire.

Les sous-instructions sont présentées dans l’annexe :

Sous-instruction1

Description

Fetch 1 et 2; PC –> Bus d’adresse

Mettre l’adresse de l’instruction LOAD R0, MaVar sur

le bus d’adresse

Fetch 3; Contrôle

Activer la ligne de lecture de la mémoire

Fetch 4,5; Bus de données –> IR

Mettre l’instruction provenant de la mémoire dans le

registre d’instruction

Load 1,2; IR –> Bus d’adresse

Mettre l’adresse de la variable contenue dans

l’instruction sur le bus d’adresse

Load 3; Contrôle

Activer la ligne de lecture de la mémoire

Load 4, 5; Bus de données –> R0

Mettre la donnée provenant de la mémoire dans R0

1

Les noms et les numéros des sous-instructions proviennent de l’annexe du cours 5

PC = PC + 1 instruction

Passer automatiquement à l’instruction suivante

Fetch 1 et 2; PC –> Bus d’adresse

Mettre l’adresse de l’instruction ADD R0, R0, R0 sur

le bus d’adresse

Fetch 3; Contrôle

Activer la ligne de lecture de la mémoire

Fetch 4,5; Bus de données –> IR

Mettre l’instruction provenant de la mémoire dans le

registre d’instruction

Add 1; ALU

Additionner R0 avec R0

Add 2; ALU

Mettre le résultat dans R0

PC = PC + 1 instruction

Passer automatiquement à l’instruction suivante

Cours 6 : ARM, 8086 et Cie

Q6.1 Les microprocesseurs ARM sont-ils vendus comme les microprocesseurs d’Intel pour

PC?

Non, les microprocesseurs ARMs sont intégrés à l’intérieur de microcontrôleurs.

Q6.2 Le cœur ARM a-t-il une architecture CISC ou RISC?

RISC.

Q6.3 Le cœur ARM a-t-il un pipeline?

Oui. L’exécution de chaque instruction se fait en trois étapes.

Q6.4 Pourquoi peut-on dire que le microprocesseur ARM est un microprocesseur 32 bits?

La plupart des paramètres d’opération du microprocesseurs valent 32 bits : largeur d’un mot de données = 32

bits, registres de 32 bits, instructions de 32 bits, adresses de mémoire sur 32 bits, et plus…

Q6.5 Qu’est-ce qu’une architecture LOAD/STORE?

Une architecture LOAD/STORE est une architecture dans laquelle un nombre très limité d’instructions permet

d’accéder à la mémoire (instructions LOAD et STORE seulement).

Q6.6 Comment modifie-t-on les drapeaux de l’ALU?

En exécutant une instruction arithmétique ou logique!

Q6.7 À quoi sert le Barrel Shifter du cœur ARM?

Il sert à décaler vers la gauche ou vers la droite les bits d’un registre en plus des autres opérations de l’ALU.

Q6.8 Quels jeux d’instructions sont supportés par le cœur ARM?

Les jeux d’instructions ARM, Thumbs, Thumb2 et Jazelle. Notez que ce ne sont pas tous les processeurs ARMs

qui supportent tous les jeux d’isntructions. En fonction de la famille du cœur, les jeux d’instructions changent.

Q6.9 Pourquoi supporte-t-on des instructions 16 bits en plus des instructions ARM 32 bits?

Pour permettre de faire des programmes plus petits et plus denses.

Q6.10 Combien d’adresses de mémoires ou de périphériques sont disponibles pour le

processeur ARM

2^32 = 4 Giga addresses (4*1024*1024*1024)

Q6.11 Le 8086 a-t-il une architecture CISC ou RISC?

CISC

Q6.12 Le 8086 a-t-il un pipeline?

Non

Q6.13 Décrivez les 40 pins du 8086 (Notez bien que quelques pins sont décrites dans les

cours 8, 9, 10 et 11).

16 lignes de données/adresse avec 2 rôles (A0-A15)

4 lignes d’adresse (A16-A19)

11 lignes pour gérer le mode, les latchs des bus de données/adresses et les bus eux-mêmes (pins 22 + 25 à 34)

3 lignes d’alimentation (GND, GND, VCC)

4 lignes pour les interruptions (NMI, INTR, RESET, INTA)

1 ligne d’horloge (CLK)

1 lignes pour tester le chip (TEST)

Q6.14 Pourquoi le 8086 a-t-il un buffer d’instruction de 6 bytes?

Les instructions sont de longueur variables.

Q6.15 A quoi sert le « transceiver » dans le schéma du mode minimum à l’intérieur de la

« datasheet » du 8086?

Même rôle que MDR. Interface pour transférer les données du CPU au bus de données.

Q6.16 Dans quel ordre et quelles pins du 8086 sont activés tour à tour afin de lire une

donnée ou une instruction en mémoire? Pour écrire?

Voir l’acétate 4 du cours 6.

Q6.17 Comment le 8086 distingue-t-il la mémoire des périphériques au niveau du bus de

contrôle?

Il se sert de la ligne M/IO.

Q6.18 Avec combien d’adresses de mémoire le 8086 peut-il communiquer? Avec combien

d’adresses d’I/O?

2^20 adresses de mémoire.

2^16 adresses d’I/O.

Q6.19 Quel est le premier microprocesseur d’Intel à…

a) … contenir un pipeline?

80486, 1989

b) … des améliorations au pipeline comme les prédicateurs de saut?

Pentium, 1993

c) … contenir une cache?

8086 si on considère le buffer d’instruction comme une cache en 1979, sinon le 286 en 1982

d) … contenir deux caches

Pentium Pro, 1995

e) … être superscalaire?

Pentium, 1993

f) … permettre l’exécution du jeu d’instruction MMX?

Pentium MMX

g) … permettre l’exécution du jeu d’instruction IA-64?

Itanium

h) … contenir deux unités de contrôle?

Dual-Core

i) … contenir un bus PCI?

Pentium, 1993

j) …traiter les fractions avec un coprocesseur dédié?

80486, 1989

Pour tous les microprocesseurs trouvés, donnez les années d’apparition.

Voir plus haut…

Q6.20 Quelle(s) broche(s) du 8086 servent à signaler une interruption au microprocesseur?

INTR, NMI et RESET

6

6

7

7

1

/

7

100%