Architecture Matérielle des Systèmes informatiques.

Architecture Matérielle des Systèmes Informatiques STS Informatique de Gestion, 1ère année

T2D1. Les différentes formes de mémoire. 1

Architecture Matérielle des Systèmes informatiques.

S1S1

BTS Informatique de Gestion

1ère année

THEME 2

:

L’ARCHITECTURE D’UN ORDINATEUR

Dossier 1

Les différentes formes de mémoire.

Objectifs

Connaître les technologies des barrettes mémoires et des autres mémoires.

Plan de la séquence

1 La mémoire vive de l’ordinateur.

1.1. Les barrettes mémoire.

1.2. Les barrettes SIMM.

1.3. Les barrettes DIMM.

2. Les différents types de RAM.

2.1. La DRAM.

2.2. La SDRAM.

2.3. la SRAM.

2.4. Comparatif des différentes technologies de barrettes mémoires.

3. Les autres mémoires.

3.1. La mémoire vidéo VRAM.

3.2. La mémoire des paramètres CMOS.

3.3. La mémoire cache.

Architecture Matérielle des Systèmes Informatiques STS Informatique de Gestion, 1ère année

T2D1. Les différentes formes de mémoire. 2

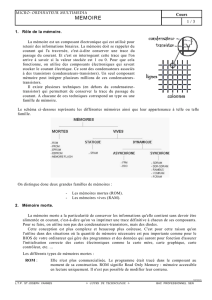

1. La mémoire vive de l’ordinateur.

Il existe de nombreux types de mémoires vives. Celles-ci se présentent toutes sous la forme de barrettes

de mémoire enfichables sur la carte-mère.

1.1. Les barrettes mémoires.

Les premières mémoires se présentaient sous la

forme de puces appelées DIP (Dual Inline

Package).

Désormais les mémoires se trouvent

généralement sous la forme de barrettes, c'est-à-

dire des cartes enfichables dans des connecteurs

prévus à cet effet. On distingue deux types de

barrettes de RAM : les barrettes au format

SIMM (Single Inline Memory Module) et les

barrettes au format DIMM (Dual Inline

Memory Module) : ce sont des circuits imprimés

possédant respectivement sur une ou deux faces

des puces de mémoire.

1.2. Les barrettes SIMM.

Les barrettes au format SIMM (Single Inline Memory Module) ne possèdent de puces de mémoire que sur

un seul côté. Il existe deux types de barrettes SIMM, selon le nombre de connecteurs :

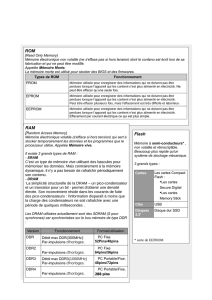

Les barrettes SIMM à 30 connecteurs (dont les dimensions sont

89x13mm) sont des mémoires 8 bits qui équipaient les premières

générations de PC (286, 386).

Les barrettes SIMM à 72 connecteurs (dont les dimensions sont

108x25mm) sont des mémoires capables de gérer 32 bits de données

simultanément. Ces mémoires équipent des PC allant du 386DX aux

premiers pentiums. Sur ces derniers, le processeur travaille avec un

bus de données d'une largeur de 64 bits, c'est la raison pour laquelle

il faut absolument équiper ces ordinateurs de deux barrettes SIMM.

Il n'est pas possible d'installer des barrettes 30 broches sur des emplacements à 72 connecteurs dans la

mesure où un détrompeur (encoche au centre des connecteurs) en empêche l'enfichage.

1.3. Les barrettes DIMM.

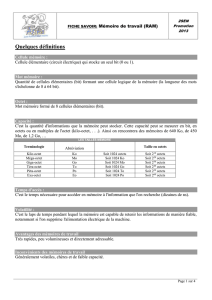

Les barrettes au format DIMM (Dual Inline Memory Module) sont

des mémoires 64 bits, ce qui explique pourquoi il n'est pas nécessaire

de les apparier. Les barrettes DIMM possèdent des puces de

mémoire de part et d'autre du circuit imprimé et ont également 84

connecteurs de chaque côté, ce qui les dote d'un total de 168 broches.

En plus de leurs dimensions plus grandes que les barrettes SIMM,

(130x25mm) ces barrettes possèdent un second détrompeur pour éviter la confusion.

A noter que les connecteurs DIMM ont été améliorés afin de permettre une insertion facile des barrettes

grâce à des leviers situés de part et d'autre du connecteur.

Architecture Matérielle des Systèmes Informatiques STS Informatique de Gestion, 1ère année

T2D1. Les différentes formes de mémoire. 3

2. Les différents types de RAM.

Il existe principalement trois types de RAM :

La DRAM, la SRDAM et la SRAM.

2.1. La DRAM.

Les accès mémoire se font généralement sur des données rangées consécutivement en mémoire. Ainsi le

mode d'accès en rafale (burst mode) permet d'accéder aux trois données consécutives à la première, sans

temps de latence supplémentaire. Le temps de latence est dû à la recherche et au positionnement de la

lecture. Dans ce mode en rafale, le temps d'accès à la première donnée est égal au temps de cycle auquel

il faut ajouter le temps de latence, et le temps d'accès aux trois autres données est uniquement égal aux

temps de cycle, on note donc sous la forme X-Y-Y-Y les quatre temps d'accès, par exemple la notation 5-

3-3-3 indique une mémoire pour laquelle 5 cycles d'horloge sont nécessaires pour accéder à la première

donnée et 3 pour les suivantes. Les 5 cycles correspondent donc à un temps de latence de 2 cycles et une

lecture de 3 cycles, comme pour les autres données.

La DRAM (Dynamic RAM, RAM dynamique) est la plus ancienne mémoire utilisée, toujours sur des

barrettes SIMM.

Il s'agit d'une mémoire dont les transistors sont rangés dans une matrice selon des lignes et des colonnes.

Un transistor, couplé à un condensateur donne l'information d'un bit. 1 octet comprenant 8 bits, une

barrette de mémoire DRAM de 16 Mo contiendra donc

..............................................= .......................... octets

soit............................................. = .........................bits

donc...........................................transistors.

Trois générations ont vu le jour, chaque fois après une amélioration au niveau des techniques d’accès aux

données.

La DRAM FPM (barrettes SIMM 30 connecteurs)

La DRAM EDO (barrettes SIMM 72 connecteurs).

Dans la mesure où la mémoire EDO n'acceptait pas des fréquences supérieures à 66 Mhz, elle a disparu

au bénéfice de la SDRAM.

2.2 La SDRAM (barrettes DIMM).

Ø La SDRAM (Synchronous DRAM, traduisez RAM synchrone), apparue en 1997, permet une lecture

des données synchronisée avec le bus de la carte-mère, contrairement aux mémoires EDO et FPM

(qualifiées d'asynchrones) possédant leur propre horloge. La SDRAM permet donc de s'affranchir des

temps d'attente dus à la synchronisation avec la carte-mère. Celle-ci permet d'obtenir un cycle en mode

rafale de la forme 5-1-1-1, c'est-à-dire un gain de 3 cycles par rapport à la RAM EDO. De cette façon,

la SDRAM est capable de fonctionner avec une cadence allant jusqu'à 150Mhz, lui permettant

d'obtenir des temps d'accès d'environ 10ns.

Ø La DDR-SDRAM (Double Data Rate SDRAM) est une mémoire fondée sur la technologie SDRAM,

permettant de doubler le taux de transfert de la SDRAM à fréquence égale.

Architecture Matérielle des Systèmes Informatiques STS Informatique de Gestion, 1ère année

T2D1. Les différentes formes de mémoire. 4

Ø La DR-SDRAM (Direct Rambus SDRAM ou encore RDRAM) est un type de mémoire permettant de

transférer les données sur un bus de 16 bits de largeur à une cadence de 800Mhz, ce qui lui confère une

bande passante de 1,6 Go/s. Comme la SDRAM, ce type de mémoire est synchronisé avec l'horloge du

bus pour améliorer les échanges de données. En contrepartie, la mémoire RAMBUS est une

technologie propriétaire, ce qui signifie que toute entreprise désirant construire des barrettes de RAM

selon cette technologie doit reverser des droits (royalties) aux sociétés RAMBUS et Intel.

Les barrettes utilisées sont spécifiques et nommées RIMM (Rambus In-Line Memory Module).

La RDRAM, apparue en 1999, était la première mémoire de type DDR commercialisée

en grande série. Elle devait être la mémoire de prédilection du Pentium 4 mais

le fait que Rambus contrôlait les brevets et pratiquait des tarifs plutôt

élevés a fait que la DDR standard s’est généralisée.

Le DR-SDRAM a évolué pour devenir la XDR-DRAM

et maintenant la XDR2-DRAM.

La XDR et la XDR2 sont des évolutions de la RDRAM. Elles ont une latence réduite et présentent des

performances plus élevées que la DDR2 ou la DDR3. Elles n’ont pas équipé de cartes mères de PC mais

on les retrouve dans des cartes graphiques haut de gamme ou dans les mémoires des PlayStation 2 et 3 de

Sony.

Intel semble intéressé par cette technologie pour ses futurs processeurs 32 nm, mais rien n'a encore été

décidé.

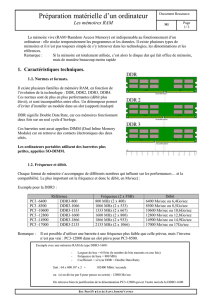

2.3. La SRAM.

L’inconvénient des DRAM réside dans le fait qu'elles sont dynamiques. Elles sont composées de

condensateurs qui se déchargent spontanément. Il faut donc les rafraîchir (les re-remplir).

La mémoire statique SRAM (Static RAM) ne nécessite pas de rafraîchissement. Elle est, en outre,

beaucoup plus rapide que la mémoire dynamique. Elle équipe toutes les mémoires flash (appareils photos,

clé USB, cartes bancaires ou vitales, …)

2.4. Comparatif des différentes technologies de barrettes mémoires.

J Les barrettes SIMM.

Barrette Fréquence Bande passante

maximale

FPM 33 Mhz 178 Mo/s

SIMM

EDO 33 MHz 264 Mo/s

J Les barrettes DIMM.

Pour les barrettes DIMM, il est possible de calculer leur bande passante (leur capacité de transfert de

données en une seconde) ainsi :

Fréquence réelle = ..........................................................................................................

Bande Passante = ..........................................................................................................

Architecture Matérielle des Systèmes Informatiques STS Informatique de Gestion, 1ère année

T2D1. Les différentes formes de mémoire. 5

J Les barrettes DIMM SDRAM.

Les barrettes SDRAM n'ont qu'un seul canal, un bus de 64 bits.

Leur nom commercial commence par PC et est suffixé de leur fréquence.

Barrette Fréquence Bande passante

maximale Nom commercial

66 Mhz

100 Mhz

133 Mhz

DIMM

SDRAM

150 Mhz

J Les barrettes DIMM DDR.

Le nom commercial de ces barrettes commence par PC, suffixé de leur bande passante.

Il arrive que PC soit suivi d'un 2 pour la DDR II et d'une 3 pour la DDR III.

Enfin, la DDR I possède 2 canaux, la DDR II possède 4 canaux et la DDR III possède 8 canaux.

Fréquence (MHz)

Barrette du bus

réelle Bande passante

maximale Nom commercial

100

133

150

166

DDR-

SDRAM

DDR

DDR I 200

133

166 DDR II 200

133

166

DIMM

DDR III

200

J Les barrettes Rambus.

Ce sont des RAM travaillant sur un bus de 16 bits.

Barrette Fréquence (MHz) Bande passante

maximale

3200

4000

XDR DRAM

4800

XDR2 DRAM 8000

6

6

1

/

6

100%