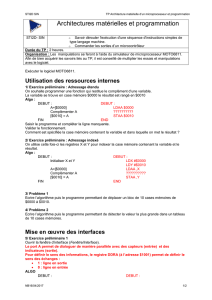

Unité Centrale 4 bits

Unité Centrale 4 bits

architecture d’un ordinateur

c

Jacques Duma

19 octobre 2012

Ce document décrit l’architecture d’un tout petit ordinateur très simple

basé sur un processeur 4 bits.

L’application Web "UC4bits" simule cet ordinateur et permet de le faire

fonctionner de façon interactive :

Pour montrer les fonctions disponibles sur cet ordinateur et expliquer

comment les utiliser, on présente d’abord section 1 un exemple très simple

que l’on réalise pas à pas.

On décrit ensuite avec précision section 2 l’architecture de la machine,

ses registres et sa mémoire.

Puis on définit section 3 l’ensemble des seize instructions du langage de

programmation machine.

Un mode d’emploi de l’application est présenté section 4.

Enfin, pour terminer, on propose section 5 d’autres exemples classés par

ordre de difficulté croissante.

1

Table des matières

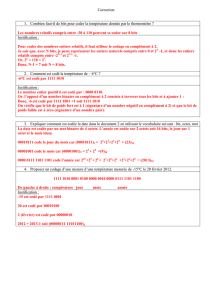

1 Exemple simple 4

1.1 Le problème ............................ 4

1.2 Algorithme de résolution du problème .............. 4

1.3 Adaptation de l’algorithme au processeur ............ 5

1.4 Écriture de l’algorithme en langage machine .......... 6

1.5 Codage de l’algorithme en binaire ................ 7

1.6 Programmation de la machine et tests ............. 7

1.7 Test de l’algorithme ........................ 7

1.8 Résumé .............................. 8

2 Architecture de la machine 8

2.1 Registres du processeur ...................... 9

2.1.1 Registres de contrôle ................... 9

2.1.2 Registre de calcul et bascule de débordement ..... 10

2.1.3 Registre d’Entrée/Sortie ................. 10

2.2 Mémoire .............................. 11

2.3 Cycle d’exécution des instructions ................ 11

3 Langage machine 11

3.0 0000 : STOP ........................... 12

3.1 0001 : JIFOVR Jump if overflow ............... 13

3.2 0010 : JUMP ........................... 13

3.3 0011 : JIFZ Jump if zero ................... 13

3.4 0100 : JIFNZ Jump if not zero ................ 13

3.5 0101 : READ ........................... 14

3.6 0110 : WRITE ........................... 14

3.7 0111 : LDA Load A...................... 15

3.8 1000 : STA Store A...................... 15

3.9 1001 : ADDA Add A...................... 15

3.10 1010 : SUBA Subtract A.................... 15

3.11 1011 : INC Increment ..................... 16

3.12 1100 : DEC Decrement .................... 16

3.13 1101 : LSHIFT Left shift ................... 16

3.14 1110 : RSHIFT Right shift .................. 17

3.15 1111 : CMPL Complement ................... 17

4 Mode d’emploi de l’application 18

4.1 Programmation .......................... 18

4.2 Exécution ............................. 18

2

4.3 Assembleur ............................ 19

5 Autres exemples 21

5.1 Complémenter bit à bit ...................... 21

5.2 Clignoter les diodes N fois .................... 22

5.3 Additioner de deux entiers .................... 23

5.4 Tripler un nombre sans retenue ................. 25

5.5 Tripler un nombre avec retenue ................. 27

5.6 Multiplier deux nombres ..................... 29

5.7 Somme des N premiers entiers .................. 32

3

1 Exemple simple

Cette Unité Centrale 4 bits contrôle une mémoire de 16 octets dans la-

quelle on peut coder de petits programmes écrits à l’aide d’un jeu de 16

instructions machine.

Un premier exemple simple va être décrit en détail pour montrer ce qu’il

est possible de faire avec ce minuscule ordinateur.

1.1 Le problème

On se propose de lire deux nombres et d’afficher le plus grand.

En réalité, on se propose d’écrire un petit programme que l’on enregistrera

dans la mémoire de la machine. On lancera alors l’exécution de ce petit

programme. Et, en principe, il devra résoudre le problème.

Donc, précisons d’abord le sens que l’on donne à tous les mots du problème

qui a été proposé ci-dessus :

– on appelle nombre un entier compris entre 0 et 255, c’est à dire un

entier qu’il est possible de coder en binaire sur un octet.

–lire signifie que lors de l’exécution du programme une interruption se

produira pour permettre à l’utilisateur de donner un nombre à la ma-

chine qui pourra alors le lire, c’est à dire l’enregistrer dans sa mémoire.

–afficher signifie que lors de l’exécution du programme une interrup-

tion se produira pour permettre à la machine d’afficher un octet de sa

mémoire.

Les opérations d’enregistrement dans la mémoire, de lecture ou d’affi-

chage aussi appelée Entrées/Sorties, se font sur le Panneau de commande

présenté page 18, à l’aide de 8 diodes bleues (les 8 bits d’un octet) qu’il est

possible d’allumer (mettre à 1) ou d’éteindre (mettre à 0) avant de valider la

configuration.

La conception du programme va s’effectuer pas à pas, en langage courant

d’abord, de façon symbolique ensuite, puis enfin en codant le problème en

binaire comme l’exige la machine.

On découvrira ainsi petit à petit le principe des contraintes imposées par

l’utilisation d’un ordinateur.

1.2 Algorithme de résolution du problème

Un minimum d’expérience en algorithmique permet assez facilement de

décrire la solution du problème :

4

Lire M

Lire N

Si M > N alors

Afficher M

Sinon

Afficher N

Fin

Si l’on consulte la liste des instructions disponibles section 3 page 11 on

constate l’absence d’un test de supériorité.

Pour tester que M>Nil sera nécessaire de calculer la différence M−Net

de tester que cette opération s’est déroulée sans débordement.

En informatique on parle de débordement (ou overflow ) lorsqu’une opéra-

tion arithmétique dépasse la capacité du processeur. Dans notre cas, comme

on traite uniquement des entiers compris entre 0 et 255, un débordement se

produira dans le calcul de M−Nsi N>M.

1.3 Adaptation de l’algorithme au processeur

On va réécrire l’algorithme, toujours dans un langage symbolique, mais

plus proche de celui de la machine. Dans ce qui suit, les variables représentées

par les lettres Met Nreprésente des octets de la mémoire, mais certaines

contraintes liées à l’architecture de la machine apparaissent.

Comme il n’existe pas de test de supériorité, il faudra le remplacer par

une soustraction et un test de débordement.

Selon le résultat du test, la suite du programme sera située à deux endroits

distincts de la mémoire, donc il sera nécessaire d’effectuer un saut à une

adresse particulière de la mémoire que l’on va étiqueter.

Comme il n’est pas possible de soustraire directement des octets de la

mémoire, il faudra utiliser le registre de calcul de l’unité centrale. Ce registre

nommé Aest décrit sous-section 2.1.

L’algorithme de résolution du problème va prendre la fore suivante :

Lire M

Lire N

A←M

A←A - N

Saut_Si_Débordement

Aller_à SUITE

Afficher N

Stop

SUITE Afficher M

Stop

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

1

/

35

100%