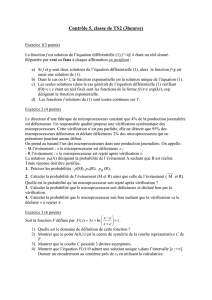

Architecture des Systèmes Programmés Architectures

septembre 09 Microprocesseurs d’usage général : Introduction ; J. Weiss 1

Architecture des

Systèmes Programmés

(6 conférences)

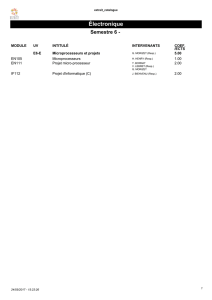

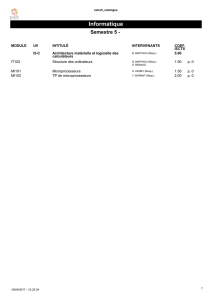

Architectures CISC et VLIW : J.Weiss 4 conférences

Microprocesseurs 8, 16 et 32 bits d’usage général (8080, ..., Pentium 4)

Microcontrôleurs 8 et 16 bits (68hc11, 8051 et PIC)

Nouvelles architectures (Itanium, IA64 et TransMeta)

Processeurs graphiques (GPU)

Mémoires

Architectures RISC et DSP : P. Leray 2 conférences

Processeurs RISC (PowerPC, Alpha, ...)

DSP (TMS320, 56000, ...)

Bus de communications

septembre 09 Microprocesseurs d’usage général : Introduction ; J. Weiss 2

Architectures

ZISC : Zero Instruction Set Computer

Autrement dit : Processeur Câblé (et donc PAS programmé)

CISC : Complex Instruction Set Computer

Processeur possédant un jeu d’instructions fourni de longueur

et de temps d’exécution variables.

VLIW : Very Long Instruction Word

Processeur possédant un jeu d’instructions encore plus fourni

que le cas du CISC (longueur et temps d’exécution variables).

RISC : Reduced Instruction Set Computer

Processeur possédant un jeu d’instructions réduit de longueur

et de temps d’exécution fixes

Page 1

septembre 09 Microprocesseurs d’usage général : Introduction ; J. Weiss 3

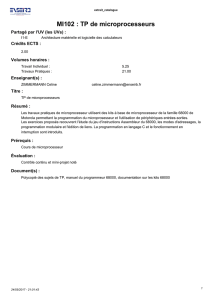

Microprocesseurs d’usage général

à architecture CISC

Architecture de base des microprocesseurs

Historique de l’informatique et des Microprocesseurs

ALU, Registres

Composants périphériques

Microprocesseurs et Microcontrôleurs 8 bits

Microprocesseurs 16 bits

Gestion de mémoire virtuelle, caches

Microprocesseurs 32 bits

1ère Génération : 80386, 68020

2ème Génération : Pentium

3ème Génération : Pentium Pro, Pentium II

4ème Génération : Pentium 4, TransMeta

Microprocesseurs 64 bits

septembre 09 Microprocesseurs d’usage général : Introduction ; J. Weiss 4

50 ans d’histoire de

l’industrie informatique

ENIAC :

1er Ordinateur

1947

Mise au point

du transistor

1948

1er ordinateur

IBM

1955

Fondation de

Fairchild SC

1957

Invention du

circuit intégré

(Kilby et Noyce)

1958-59

Mini-ordinateur

DEC

1963

Fondation

d’Intel

1968

1971

1er µP

1ère EPROM

Intel

Fondation de

Microsoft

1975

1977

Apple II

1981

IBM-PC

1985

386

1989

486

1993

Pentium

1997

Pentium II

2000

Pentium 4

Page 2

septembre 09 Microprocesseurs d’usage général : Introduction ; J. Weiss 5

État de l’informatique en 1968

1948 : 1er ordinateur : ENIAC (30 tonnes 85 m3)

(Electronic Numerical Integrator And Computer)

1968 : 30.000 ordinateurs dans le monde :

Mainframes (plusieurs pièces)

Mini-ordinateurs (taille d’un réfrigérateur)

Programmation : Cartes et bandes perforées

septembre 09 Microprocesseurs d’usage général : Introduction ; J. Weiss 6

Historique des

Microprocesseurs CISC

1960 Premiers CI

1964 SSI AND, OR

1968 MSI Registres

1971 LSI DRAM 1 kbits, µP 4 bits (4004 d’Intel)

2,3 kT 1972 8 bits 1ère G. 8008 (Intel)

1973 8 bits 2ème G. 8080 (Intel), 6800 (Motorola)

1975 8 bits 3ème G. 8085 (Intel), 6809 (Motorola), Z80 (Zilog)

1976 16 bits 1ère G. TMS 9900 (Texas Instruments)

1978 16 bits 1ère G. 8086 (Intel) IBM-PC/XT

1979 16 bits 1ère G. 68000 (Motorola) MAC

1982 16 bits 2ème G. 80286 (Intel) IBM-PC/AT

1983 32 bits 1ère G. 32032 (National)

1984 32 bits 1ère G. 80386 (Intel), 68020 (Motorola)

1987 32 bits 1ère G. 68030 (Motorola) SUN3

1989 32 bits 2ème G. 80486 (Intel)1,2 MT 1993 32 bits 3ème G. Pentium (Intel)

1995 32 bits 3ème G. PentiumPro (Intel)

1997 32 bits 3ème G. Pentium II (Intel)

5,5 MT

2000 32 bits 4ème G. Pentium 4 (Intel)

42 MT 2007 32 bits 4ème G. Core 2 Quad (Intel)

580 MT 2008 64 bits 2ème G. Itanium 2 dual core (Intel)

1900 MT

Page 3

septembre 09 Microprocesseurs d’usage général : Introduction ; J. Weiss 7

Création d’Intel :

les «Fairchildren»

Bob Noyce : Fondateur

Invention du circuit intégré en 1959

Fondateur et ex dirigeant de Fairchild Semiconductor

Gordon Moore : Fondateur

Invention du circuit intégré en 1959

Fondateur et ex responsable R&D de Fairchild Semiconductor

Andy Grove : N°4 d’Intel

Docteur en Chimie

Ex responsable de fabrication de Fairchild Semiconductor

septembre 09 Microprocesseurs d’usage général : Introduction ; J. Weiss 8

Les débuts d’Intel

1969 : mémoires SRAM 64 bits (bipolaire)

1970 : conception du premier microprocesseur :

4004 pour Busicom (Japon) :

Technologie MOS 10 µm 3,17*4,23 mm²

2300 T

1971 : Commercialisation du premier microprocesseur : 4004

Page 4

septembre 09 Microprocesseurs d’usage général : Introduction ; J. Weiss 9

Succès d’un produit

Le succès d’un produit est lié à :

Diffusion : Microinformatique (x86)

Marchés militaires (Z80.000)

Marchés captifs (Rockwell, Comodore)

Prix : existence de 2ndes Sources

Environnement : existence de périphériques

de systèmes de développement

Arrivée sur le marché

Notion de «famille» : x86, 680x0

septembre 09 Microprocesseurs d’usage général : Introduction ; J. Weiss 10

Technologie des microprocesseurs

Loi de Moore

Nombre de transistors

Temps

1 k

10 k

100 k

1 M

10 M

100 M

1970 1975 1980 1985 1990 1995 2000

4004 8080

8086

286 386

486 Pentium

Pentium II

Pentium 4

Page 5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

1

/

20

100%