CONCEPTION DES CIRCUITS INTEGRES

Première partie : LE TRAVAIL DU SILICIUM

I - CONCEPTION DES CIRCUITS INTEGRES..

1 - Rappels sur la jonction PN 1

1- 1 - Atomes, liaisons atomiques 1

1 - 1 - 1 - Les gaz rares 1

1 - 1 - 2 - Les liaisons métalliques 2

1 - 1 - 3 - Les liaisons ioniques 2

1 - 1 - 4 - Les liaisons covalentes 3

1 - 2 - Les Semi-Conducteurs 3

1 - 2 - 1 - Le Silicium dopé "N" 3

1 - 2 - 2 - Le Silicium dopé "P" 3

1 - 3 - La jonction ................................................................................................4

1 - 4 - La jonction Métal - Semiconducteur 6

I - 2 - Le Transistor Bipolaire ……………………………………………………………………….7

I - 3 - Le Transistor à effet de champ ......................................................................................... 8

I - 3 - 1 - Le Transistor à effet de champ à jonctions JFET ........................................................... 8

I - 3 - 2 - Le Transistor à effet de champ MOS à appauvrissement (Déplétion) .......................... 10

I - 3 - 3 - Le Transistor à effet de champ MOS à enrichissement (Enhancement) ...................... 11

I - 4 - La fabrication des circuits intégrés ................................................................................ 11

I - 4 -1 - La réalisation des monocristaux de Silicium ................................................................... 12

I - 4 - 2 - Purification des monocristaux de Silicium ..................................................................... 13

I - 4 - 3 - Sciage des plaquettes de Silicium ................................................................................. 13

I - 4 - 4 - Dopage du Silicium ........................................................................................................ 13

I - 4 - 4 - 1 -Nature -des dopants .................................................................................................. 13

I - 4 - 4 - 2 Techniques ................................................................................................................. 13

I - 4 - 4 - 2 - 1 L'épitaxie ............................................................................................................... 13

I - 4 - 4 - 2 - 2 Diffusion ............................................................................................................... 13

I - 4 - 4 - 2 - 3 Implantation ionique ............................................................................................. 14

I - 4 - 4 - 3 Le masquage .............................................................................................................. 14

I - 4 - 4 - 4 L'oxydation .................................................................................................................. 16

I - 4 - 4 - 5 Les interconnexions et dépôts conducteurs ............................................................... 16

I - 4 - 4 - 6 Réalisation des circuits intégrés à base de transistors bipolaires ............................. 16

I - 4 - 4 - 7 Réalisation des circuits intégrés à base de transistors MOS à enrichissement ........ 18

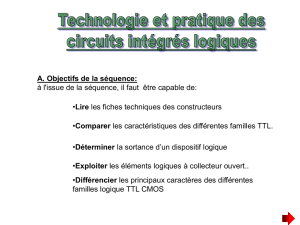

Deuxième partie : Choisir une technologie

II - TECHNOLOGIES DES CIRCUITS INTEGRES ..................................................................... 20

II - 1 - Critères de choix des différentes technologies ............................................................ 20

II - 1- 1 - Le prix ............................................................................................................................ 20

Il - 1 - 2 - La fiabilité ...................................................................................................................... 21

II - 1 - 3 - La rapidité ..................................................................................................................... 21

II - 1 - 4 - Consommation ............................................................................................................. 22

II - 1 - 5 - Immunité au bruit ......................................................................................................... 22

Troisième partie : les technologies à transistors bipolaires saturés

II - 2 - Les différentes technologies .......................................................................................... 24

II - 2 - 1 - Technologies à base de Transistors Bipolaires Saturés .............................................. 24

II - 2 - 1 - 1 La technologie DTL .................................................................................................. 24

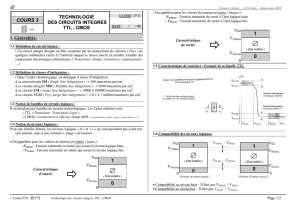

II - 2 - 1 - 2 La technologie TTL .................................................................................................. 26

II - 2 - 1 - 2- 1 - L'inverseur TTL standard ................................................................................... 26

II - 2 - 1 - 2- 2 - L'inverseur TTL Trigger de Schmit ..................................................................... 27

II - 2 - 1 - 2- 3 - La porte Nand TTL standard .............................................................................. 28

II - 2 - 1 - 2- 3 - 1Caractéristiques de la porte TTL std et ses deux sous familles H S et L P ..... 28

II - 2 - 1 - 2- 3 - 2Les références TTL .......................................................................................... 30

II - 2 - 1 - 3 La technologie TTL Schottky .................................................................................... 30

II - 2 - 1 - 4 La technologie TTL Schottky Avancée ..................................................................... 32

II - 2 - 1 - 5 Les sorties des portes TTL ....................................................................................... 33

II - 2 - 1 - 5 - 1 - La sortie Totem Pole ......................................................................................... 33

II - 2 - 1 - 5 - 2 -La sortie à collecteur ouvert (Open Collector) .................................................... 34

II - 2 - 1 - 5 - 3 - La sortie trois états ( Tri Stats ) ......................................................................... 37

Quatrième partie : les technologies à transistors bipolaires non saturés

II - 2 - 2 - Technologie à transistors bipolaires non saturés ........................................................ 37

II - 2 - 2 - 1 - Base de la technologie ECL ................................................................................... 37

II - 2 - 2 - 2 - La technologie ECL 10.000 (10K) .......................................................................... 39

II - 2 - 2 - 2 - 1 - Schéma de la porte de base ECL IOK .............................................................. 39

II – 2 - 2- 2 - 2 - Caractéristiques de la porte de base ECL 10K . ................................................ 40

II – 2 - 2- 3 - Technologie ECL IOOK ........................................................................................... 40

II – 2 - 2- 3 - 1 - Schéma de la porte de base ECL 100K ............................................................. 40

II – 2 - 2- 3 - 2 - Caractéristiques de la porte de base ECL 100K ................................................ 42

Cinquième partie : les technologies à transistors MOS

V - Technologie à base de transistors à effet de champ MOS ...................................................... 44

V - 1 - Un peu d'histoire des CMOS ........................................................................................ 44

V - 2 - La CMOS 4000 ............................................................................................................ 44

V - 2 - 1 - La porte de base CMOS 4000 ............................................................................... 44

V - 2 - 2 - Phénomène de Latch Up ....................................................................................... 46

V - 2 - 3 - Les CMOS 4000 en commutateurs analogiques ................................................... 47

V - 2 - 4 - Caractéristiques des CMOS 4000 ......................................................................... 48

V - 2 - 4 - 1 - Résistance ON des transistors de sortie . ....................................................... 48

V - 2 - 4 - 2 - Fréquence maximale d’utilisation .................................................................... 48

V - 2 - 4 - 3 - Immunité au bruit . .......................................................................................... 49

V - 2 - 4 - 4 - Consommation électrique ............................................................................... 50

V - 2 - 5 - Caractéristique de la porte NAND 4011 .......................................................... 50

V - 3 - La Famille CMOS 74C ........................................................................................... 51

V - 4 - La Famille CMOS HC et HCT ................................................................................ 51

V - 5 - La Famille CMOS AC et ACT ................................................................................ 52

Sixième partie : les technologies Bicmos

II – 2 – 4 - La technologie BiCMOS ............................................................................................... 53

II – 2 – 4 - 1 - Schéma de la porte NAND 74BCOO ...................................................................... 53

II – 2 – 4 - 2 - Caractéristiques de la porte NAND 74BCOO ......................................................... 53

II – 2 – 5 - Les circuits à Arséniure de Gallium ............................................................................ 54

Septième partie : les logiques basse tension

II – 3 Les circuits basse tension .................................................................................................. 54

II – 3 – 1 – Basse tension pourquoi ............................................................................................... 54

II – 2 – 2 – Présentation des familles ............................................................................................ 54

Il - 3 - Le point aujourd'hui et quelques perspectives .................................................................... 58

VII MISE EN OEUVRE DES CIRCUITS INTEGRES

VII - 1 - Généralités ...................................................................................................................... 60

VII - 2 - Entrées et Sorties ............................................................................................................ 60

VII - 2- 1 - Polarisation des entrées .............................................................................................. 60

VII - 2- 1 - 1 - Polarisation permanente ........................................................................................ 60

VII - 2- 1 - 2 - Polarisation par un composant de la même famille ............................................... 61

VII - 2- 1 - 2 - 1 - Les CMOS ......................................................................................................... 61

VII - 2- 1 – 2 - 2 - LesTTL ............................................................................................................. 63

VII - 2- 1 - 3 - Polarisation par un composant d'une autre famille ................................................ 64

VII - 2- 1 - 3 - 1 - Association CMOS 4000 ' TTL .......................................................................... 64

VII - 2- 1 - 3 - 2- Association CMOS HC ' TTL .............................................................................. 66

VII - 2- 1 - 3 - 3- Association CMOS AC ' TTL .............................................................................. 67

VII - 2- 1 - 4 - Polarisation par un composant mécanique, électromécanique ou une électronique éloignée ..68

VII – 2 - 1- 4 -1- Généralités ......................................................................................................... 68

VII - 2- 1 - 4 - 2 - Élimination des rebonds de contact .................................................................. 68

VII - 2- 1 - 4 - 3 - Protection contre les parasites .......................................................................... 70

VII - 2- 1 - 4 - 3 - 1 - Parasites générés par les relais électromagnétiques .................................. 70

VII - 2 - 1 - 4 - 3 - 2 -Commande par opto-coupleurs .............................................................. 71

1

/

3

100%