Introduc^on au parallélisme Cécile Germain‐Renaud cecile

1

!"#$%&'()%"*+'*,+$+--.-/012*

!"#$%&'(&)*+$,-.&,+/0'

#&#$%&12&)*+$,3%)$14)'

3$4+"/0+)%"*

• 56'7"+,#&7'#8/)7'&9':;<'=>'#>+#/,&'

• ?'7"+,#&7'@+)'A8B%'C+%#8/'

• D&7'7%$0&7',&'7/E7&,9'F)+$*&,9'@+7'

– G$0&'*"*8$)&'H'$%%/79)+I8,7'

– D&'#8/)7'8)+%'&79'7/@@87"'#8,,/'@8/)'%J&K+*&,'

• !+%&,0)$&)'&9'98/9&7'$,48)*+I8,7'7/)'%&'7$9&'0/'#8/)7'

L'F8/7'0&F&M'%&'#8,7/%9&)1'

2 Introduction au parallélisme

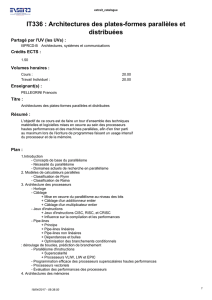

5556-$/67$89(2(/-28:;<:!=;:>:;?8!@AB*

C%"#$D-2*&20*(%""+/00+"(20*

• !8,9)N%&'#8,I,/'

– ;&/K'0&F8$)7'-'%+)2&*&,9'#8**&,#"7'&,':;1'G')&,0)&'O'%+'

0+9&'@)"F/&1'5'P8/)'0&')&9+)0'Q'-5'@8$,91';&F8$)7'

$,0$F$0/&%71''

– R,'&K@87"1'!>8$K'0+,7'S'7&*+$,&7<'&K@87"7'H'T#>&')"7/*"'

O'%+'0&),$U)&'7"+,#&1':)+F+$%'&,'V$,N*&<'%J/,'&79',89"'7/)'%+'

T#>&'0&'%	/)&<'%J+/9)&'7/)'%J&K@87"1'

• WK+*&,'

– :8/7'08#/*&,97'+/98)$7"71'X8/7'0&F&M'+*&,&)'%&7'

08#/*&,97<'",8,#"7<Y'/I%$7"7'&,'#8/)7Z:;1'

3 Introduction au parallélisme

5556-$/67$89(2(/-28:;<:!=;:>:;?8!@AB*

2

@-+"*

51 [8IF+I8,'&9'#8,#&@97'

61 G%28)$9>*$\/&'@+)+%%U%&'

?1 ])82)+**+I8,'@+)+%%U%&'

– ]+77+2&'0&'*&77+2&7'

– ^@&,[]'

=1 [80U%&7'48)*&%7'

– ]+)+%%"%$7+I8,'+/98*+I\/&''

– [80U%&7'+F+,#"7'

Introduction au parallélisme 4

E6*>%)F+)%"*2#*(%"(2,#0*

Introduction au parallélisme 5

@-+"*

• [8IF+I8,'

• G)#>$9	/)&7'@+)+%%U%&7'

– D&7'$,4)+79)/#9/)&7'@+)+%%U%&7'&,'6__`'

– :a@8%82$&'

– WK&*@%&7'

• ]&)48)*+,#&'

– G##"%")+I8,'

– G/9)&7'$,0$#+9&/)7'

Introduction au parallélisme 6

3

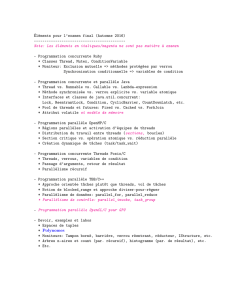

>%)F+)%"*!*G*H20*+,,-/(+)%"0*

• !"#$%&'()*)$#+,"-$.*/*.01+,".)2.3*")*3"%"2(''-'4,("3"5#.*

2(#1(3&)6.*7.*%&*32".)2.*

– :)8@'2)+,0&7'b'*"9"8)8%82$&<'*+9")$+/K<Y'

– :)8@'0+,2&)&/7&7'b'*+$,9&,+,#&',/#%"+$)&'

– :)8@'#8c9&/7&7'b'#)+7>-9&797<'#8,#&@I8,'+")8,+/I\/&'

– d*@877$V%&7'b'#%$*+9<'+79)8@>a7$\/&''

• 8)9(,#&'()*7.%$:.'

– ]/#&7'O'G;e'

– :)+$9&*&,9'@&)78,,+%$7"'

• ;+&%"6+*<",6$.%%.*($*&$:#.)6+.'b'*"0$+7<'*"0$#+%'

Introduction au parallélisme 7

I20%/"*2"*,'/00+"(2*&2*(+-('-*J(%1,')"4K*F/$#'2--212"#*/--/1/#.0*

>%)F+)%"*!!*G*H20*%$&/"+#2'$0*

Introduction au parallélisme 8

?%'#20*-20*/"7$+0#$'(#'$20*&2*(+-('-*0%"#*,+$+--L-20**

>%)F+)%"*!!!*G*H20*0%'$(20*&'*,+$+--.-/012*

• ]+)+%%"%$7*&'0&'08,,"&7'

– ;U7'\/J8,'+'0&7'9+V%&+/K'fO'@)"#$7&)g'

• ]+)+%%"%$7*&'0&'#8,9)N%&'

– h$2>':>)8/2>@/9'+@@%$#+I8,7'

– ])8#"0/)&7')"#/)7$F&7'

– .]!''

– Y'

Introduction au parallélisme 9

H20*+,,-/(+)%"0*,2'F2"#*2M,-%/#2$*-20*/"7$+0#$'(#'$20*,+$+--L-20**

4

N"*2"F/$%""212"#*-%4/(/2-*0#+O/-/0.*1+/0*"%"*

'"/P.*

10

Application

Algorithme

LHN

Environnement

d’exécution //

Programmes séquentiels

Résolution système linéaire

Relaxation, méthode directe

Spécification

Programmation

Compilateurs

parallèles

Compilateurs

+ exécutifs

OpenMP, HPF, pC++…

MPI, PVM, threads

Introduction au parallélisme

N"*2"F/$%""212"#*-%4/(/2-*0#+O/-/0.*1+/0*"%"*

'"/P.*

11

Application

Algorithme

Environnement

d’exécution //

Programmes séquentiels

Résolution système linéaire

Relaxation

Spécification

Programmation

Compilateurs

+ exécutifs

MPI, PVM, threads

Introduction au parallélisme

N"*2"F/$%""212"#*-%4/(/2-*0#+O/-/0.*1+/0*"%"*

'"/P.*

12

Application

Algorithme

LHN

Environnement

d’exécution //

Programmes séquentiels

Résolution système linéaire

Relaxation

Spécification

Programmation

Compilateurs

parallèles

Compilateurs

+ exécutifs

OpenMP, HPF, pC++…

MPI, PVM, threads

Introduction au parallélisme

5

H2*?%,*QRR*

• D&7'i__'8)0$,+9&/)7'%&7'@%/7'

@/$77+,97'

– X8%8,9+)$+9'

– 6'48$7'@+)'+,'0&@/$7'5``?1'

• WF+%/"'7/)'D$,@+#j<'/,'

V&,#>*+)j'4+#$%&'&9',8,'

9)$F$+%'

• ]&)48)*+,#&'.[+K'*&7/)"&'

&,'CD^]k'

• G'#8*@+)&)'+F&#'.]&+j<'%+'

@/$77+,#&'$,0"@+77+V%&1'

Introduction au parallélisme 13

H+*O+$$/L$2*&'*@2#+S-%,0*+*.#.*7$+"(T/2*2"*URRV**

www.top500.org

?3@*QRR*G*;%1O$2*&2*,$%(2002'$0*8*0W0#L12*

;%F21O$2**URRX*

Introduction au parallélisme 14

H2*?%,*QRR*2"*;%F21O$2*URRX**

Introduction au parallélisme 15

5WH_='

5WH_i'

5WH_S'

5WH_l'

5' 5_' 5__' 5___'

B>+M*J=S-%,0K*

Rang

]&9+C%8@7'

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

1

/

15

100%