PDF, 854 Ko

1

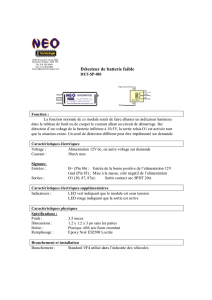

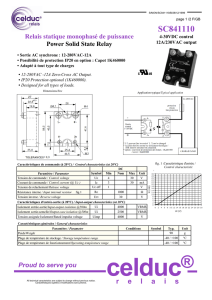

Concours technicien électronicien BAP C (mai 2011)

Les sujets peuvent être traités séparément. Vous êtes invités à aborder

l’ensemble des sujets. Vous répondrez directement sur ce document. Vous

rendrez les 20 pages du sujet en fin d’examen et conserverez les

documents annexes.

I – ETUDE D’UN SYSTEME EXPERIMENTAL

Objectif :

On souhaite effectuer des mesures de courant et de tension aux bornes d’un super

condensateur MAXWELL BPAK 15 V pour identifier ses caractéristiques.

A l’aide d’un générateur, on applique un signal constitué d’impulsions de courant de charge

et de décharge Iemc(t) provoquant des variations de tension Vemt(t) aux bornes du super

condensateur. Un exemple d’impulsion de courant de charge d’amplitude 9A est montré sur la

figure 1-1.

La figure 1-2 montre l’évolution de la tension aux bornes du super condensateur initialement

chargé à Vemt=3V. De plus, on prévoit un dispositif permettent de protéger le super condensateur en

cas de dépassement de seuils Vseuilmax et Vseuilmin (voir figure 1-2).

Figure 1-1

Figure 1-2

2

Concours technicien électronicien BAP C (mai 2011)

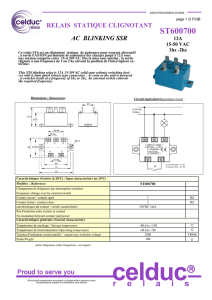

Le synoptique des différentes fonctions mises en œuvre est présenté sur la figure 2.

Dans cette étude, les amplificateurs opérationnels (AOP) seront considérés idéaux.

Ve

MC

Mesure Courant

BLOC-MT

Ie

+HT

Ve

BLOC-R

MT

Vs

-HT

BLOC-MC

DS

ds

(E )

Ve

BP2

ds

(S )

mt

BP1

D

1N4007

mt

(S )

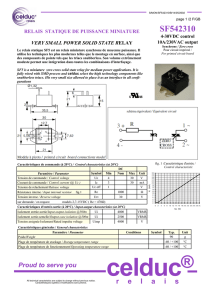

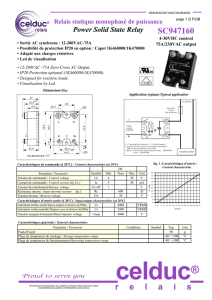

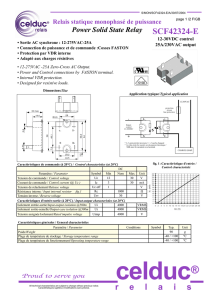

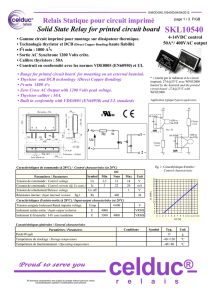

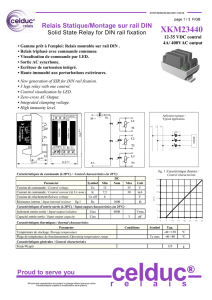

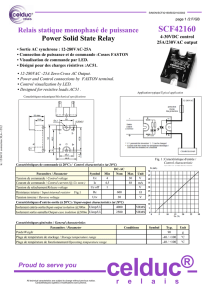

RELAIS

BLOC-DS

mc

Générateur

de courant

(I)

mc

Rdecharge

Vs

Xi

C

0V< <10V

(S )

VCC

DS

Mesure Tension

Rcharge

Ki

Détecteur de Seuils

Figure 2

Rappel : Chaque partie de ce sujet peut être traitée indépendamment des autres.

3

Concours technicien électronicien BAP C (mai 2011)

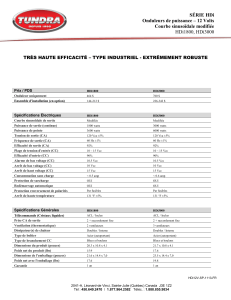

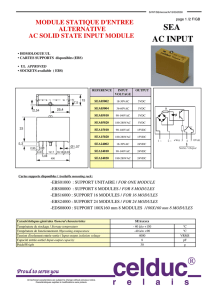

1 – Etude du BLOC-DS (Figure 3).

Ce bloc réalise la détection des seuils Vseuilmax et Vseuilmin lorsque la tension d’entrée Veds

varie.

Avec :

U1 : LM339

U2 : TL081

Rz = 270Ω, R1 = 1 kΩ, R2 = 3 kΩ, R3 = 60kΩ, R5 = R6 = 10kΩ, R7 = 100kΩ.

D1, D2 : 1N4148

Dz1/12V

C1 = C2 = C3 = 100nF.

D2

1N4148

ds

Vdd+15V

Vdd=15V

b

Vz=12V

ds

1

Vs

R5

10k

Rz

270

Vdd=15V

Vdd=15V

R2

3K

Vseuil

U1

3

a

C1

100nF

DZ1

12V

0< <+10V

R1

1K

min

max

TL0812

36

4 7

R3

60K

Vseuil

C3

100nF

Vdd=-15V

-

+

LM339

5

42

312

DS

entrée (E )

Ve

C2

100nF

2

sortie (S )

R4

?

a

Vdd=15V

Vs

-

+

LM339

7

61

312

DS

R7

100K

U1

Vdd=15V

Vs

D1

1N4148

ds

Ve

U2

R6

10K

Vs

Figure 3

1-1 – Calculer la valeur de Vseuilmax (figure 3).

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

4

Concours technicien électronicien BAP C (mai 2011)

1-2 – Déterminer la valeur R4 pour avoir Vseuilmin=0,5V

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

1-3 – Préciser le mode de fonctionnement des AOP U1a et U1b (voir doc du LM339) et préciser le

rôle des résistances R5, R6.

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

…………………………………………………………………………………………………………

1-4 – On admet le niveau de saturation haut des tensions suivantes, Vs1=13,7V, Vs2=13,7V et

Vs3=13V. Le niveau de saturation bas pour ces tensions sera de 0V. Compléter le tableau ci-dessous

en précisant l’état des diodes D1 et D2.

Vs1(V) Vs2(V) Vsds(V) D1* D2*

Veds<Vseuilmin

Vseuilmax<Veds<Vseuilmin

Veds>Vseuilmax

* P=Passante et B=Bloquée

5

Concours technicien électronicien BAP C (mai 2011)

1-5 – On suppose que le signal Veds à l’allure reportée sur la figure 4.

D’après les résultats obtenus précédemment, compléter les chronogrammes de Vs1, Vs2 et Vsds sur

la figure suivante :

Ve (V)

Vs (V)

Vs (V)

Vs (V)

T(s)

T(s)

T(s)

T(s)

9V

10V

0,5V

13,7V

13,7V

13V

ds

1

2

ds

Figure 4

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

1

/

36

100%