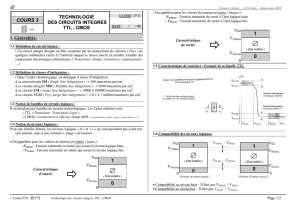

Circuits Intégrés numériques

Circuits intégrés numériques

Circuits intégrés numériques

GIF-2000

Hiver 2013

Hiver 2013

1

Familles logiques

Familles logiques

2

Famille des circuits Logique

Famille des circuits Logique

3

Familles logiques

Familles logiques

Texas Instruments, 2007

4

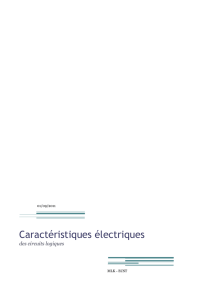

Niveaux logiques

Niveaux logiques

V

OL

(max)

-

tension

de

sortie

niveau

BAS

:

niveau

de

tension

de

V

OL

(max)

-

tension

de

sortie

niveau

BAS

:

niveau

de

tension

de

la sortie d'un circuit logique correspondant à l'état logique

0.

VOH (min) - tension de sortie niveau HAUT : niveau de tension

de la sortie d'un circuit logique correspondant à l'état

logique 1.

VIL (min): La tension d’entrée MAXIMALE pouvant être

reconnue comme un niveau d’entrée logique BAS

VIH (max): La tension d’entrée MINIMALE pouvant être

reconnue comme un niveau d’entrée logique HAUT

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

1

/

55

100%