cours d`Assembleur

Assembleur

(cours)

Architecture des ordinateurs

I. Historique

1) Les précurseurs

La création des premières machines à calculer était basée sur la technologie

des engrenages (mécaniques).

Parmi les inventeurs, il y a :

• Blaise Pascal (1623 – 1662) _ France

• Gottfried W.Phelm Leibniz (1646 – 1716) _ Allemagne

• Charles Babbage, Ada Lovelace (1792 – 1871) _ Angleterre

Jacquard : utilisation des cartes perforées (Æ machines programmables à l’aide

de cartes perforées).

Il a fallu attendre l’avènement de l’électronique pour mettre en pratique les

idées théoriques développées par les précurseurs.

En 1936 : machine de Zuse (électromécanique)

En 1940 : machine de George Stibitz (Laboratoires Bell)

En 1944 : le Mark I, université de Harvard Ai Ken avec IBM

Ces machines étaient dépassées avant même d’être construites ; au même

moment des chercheurs travaillaient sur la technologie des tubes à vide.

2) Première génération de calculateurs (1937 – 1955)

Tubes à vide

1937 : machine ABC de Atanasoff - Berry (Iowa State University)

1943 : Colossus, machine construite en Angleterre ; décodage des messages

allemands

1944 : Von Neumann étudiait le stockage des programmes sous forme

numérique avec Eckert et Mauchly :

EDVAC (=Electronic Discrete Variable Automatic Computer) = projet

de Von Neumann

1946 : ENIAC (= Electronic Numrical Integrator And Calculator), construite à

l’université de Californie :

30 mètres de long ; 2,5 m de haut ; chacun des 20 registres de 10 chiffres

avait 60 cm de long ; 18000 tubes à vide ;

la programmation se faisait manuellement en enfichant des câbles et en

positionnant des interrupteurs

1949 : Maurice Wilkes (Cambridge)

ETSAC qui fut la première machine à programmes enregistrés de

grande envergure.

Un prototype appelé le Mark I fut construit à l’université de Manchester

en 1948

1951 : Eckert et Mauchly ont construit l’UNIVACI (vendu à 48 unités)

1952 : l’EDVACI est opérationnel

1953 : 1ère machine d’IBM : IBM 701 (vendu à 19 unités)

3) Deuxième génération : transistors (1955 – 1965)

1948 : invention des transistors (Laboratoires Bell)

1961 : PDP 1 de DEC

1963 : B5000 de Bunaighs (architecture à pile) supportait les langages de haut

niveau comme l’ALGOLqui utilisait un système d’explication écrit dans

un langage de haut niveau

1964 : IBM devient n°1 avec l’IBM 7094 et l’IBM 1401 (calculateur pour gestion)

4) Troisième génération : circuits intégrés (1965 – 1980)

1964 : IBM 360 : 1ère famille d’ordinateurs à architecture commune.

CDC 6600 créé par Control Data : le 1er ordinateur pipeline

(parallélisme).

1965 : PDP 8 de DEC

1970 : PDP 11 de DEC

1978 : VAX, un seul système d’exploitation VHS, succès pendant 10 ans.

5) Quatrième génération (1980)

1980 : retour d’une architecture plus simple (Bakcley).

Ditzel et Patterson ont étudié l’idée d’ordi à jeu d’instructions réduit

(RISC).

Idée conservée par CRAY – CRAY I

1981 : PC d’IBM

1984 : Apple lance son Macintosh

1987 : Sun fournit des machines basées sur l’architecture SPARC (RISC)

1993 : Power PC

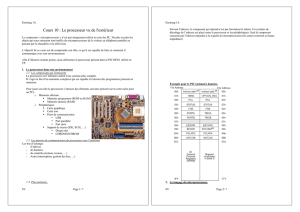

II. Architecture à microprocesseur

1) Architecture de Von Neumann

Cette machine se compose :

• d’une unité centrale (de contrôle) qui supervise le

fonctionnement de la mémoire

• d’une unité de calculs

• d’une unité d’échange (entrées / sorties)

• d’une mémoire finie

2) L’unité centrale

C’est elle qui exécute les instructions. Elle comporte des registres qui sont des

zones privilégiées de stockage de l’information (données et instructions).

Cette information sera codée dans ces registres par une suite de 0 et de 1.

8086 registres de 16 bits

80386 registres de 32 bits

Ces registres sont utilisés pour stocker :

• Les instructions arithmétiques et logiques

• L’adresse de la prochaine instruction à exécuter

• L’adresse en mémoire d’une donnée (constante stockée en mém.)

3) La mémoire

La mémoire à pour première raison d’être de fournir des registres

supplémentaires. Cette mémoire, tout comme les registres de l’unité centrale,

ne contient de façon réelle que des nombres (0 ou 1) Æ tout ce que manipule la

machine de Von Neumann doit avoir un format numérique qu’il s’agisse de

programmes ou de données (pas de distinction intrinsèque entre instruction

de programmes ou de données).

Dans la mémoire les 0 et les 1 sont regroupés par 8 (octets).

Capacité de la mémoire = nombre d’octets (1 Ko = 2^10 octets ; 1 Mo = 2^20

octets ; 1 Go = 2^30 octets).

Les octets sont considérés comme contigus et numérotés de 0 à N-1 (adresse

physique) si la mémoire est de taille MAX.

On appelle "mot mémoire" l’unité d’accès à la mémoire Æ taile des registres

du processeur.

On a plusieurs façons de coder les infos en mémoire :

Æ binaire

Æ DCB (décimal codé binaire

Æ code ASCII

Æ virgule flottante

La mémoire est décomposée en mémoire morte (qui contient le jeu

d’instructions de base du processeur) et en mémoire vive = RAM (qui contient

le programme que l’on désire exécuter).

4) Les entrées / sorties

Elles permettent l’interaction avec l’homme à travers les appareils dits

périphériques :

• Clavier

• Ecran

• Mémoire de masse (= mémoire externe), c-à-d disque dur, disquettes,

CD, …) Æ fonction de stockage de l’information. Elle possède un

caractère permanent par opposition avec la mémoire vive qui garde les

infos de façon temporaire.

5) Les bus

Ce sont des fils de communication entre l’unité centrale (U.C.), la mémoire et

les entrées / sorties :

• Bus des données Æ transporte la valeur de l’octet

• Bus d’adresse Æ fixe l’adresse de l’octet à accéder en mémoire

centrale

• Bus de contrôle Æ fixe le sens de l’échange

6) Les instructions

C’est ce qui forme le jeu d’instruction du processus :

• Instructions arithmétiques

• Instructions logiques de transfert

• Instructions de contrôle (boucle, conditionnelle)

- Architecture RISC (jeu d’instruction réduit)

- Architecture CISC (jeu d’instruction complet)

1°) recherche de l’instruction en mémoire centrale ; l’adresse est indiquée par

le compteur cardinal

• L’U.C. renvoie l’adresse de l’instruction sur le bus d’adresse et

demande une lecture sur le bus de contrôle

• La mémoire dépose la valeur contenue à cette adresse sur le bus de

données, la valeur est lue par l’U.C.

2°) décodage

• L’U.C. détermine l’instruction correspondant à la valeur lue (code) sur

le bus des données

3°) recherche de l’opérande

même principe que 1°)

4°) exécution

L’instruction n’est exécutée que si tous les opérandes sont présents ; le

résultat est gardé dans l’U.C.

Simultanément l’U.C. calcule l’adresse de la prochaine instruction à

exécuter.

5°) écriture du résultat en mémoire

principe :

• Valeur déposée sur le bus de données

• Adresse déposée sur le bus d’adresse

• Ecriture demandée sur le bus de contrôle

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

1

/

36

100%