Algorithme de Test de Mémoire pour "Neighborhood Pattern

1

Abstract— On présent un algorithme qui nous permet de

détecter les " Neighborhood Pattern sensitive Faults (NPSF)"

dans une mémoire semi-conducteur. La méthode utilisée

correspond à la utilisation d’un algorithme March à

backgrounds multiples. À l'aide de l’algorithme mentionné, on

aura la possibilité de tester les NPSF Statique, NPSF Passif et

NPSF Actif. Les algorithmes de March sont utilisés souvent pour

le test de mémoire car ils ont la caractéristique de complexité de

temps linéal et ils sont aussi faciles à réaliser en utilisant BIST.

Les algorithmes March traditionnelles ne génèrent pas tous les

patterns de voisinage pour tester tous les NPSFs, mais ils peuvent

être modifiés à l'aide d’un background de donnée multiple pour

de cette façon obtenir tous les patterns de voisinage nécessaires.

La méthode de March-12N prolongé peut détecter toutes les

sortes de fautes de mémoire (même les NPSFs) dans une durée de

test de 100N. Donc en considérant son efficacité élevée, on se

serve de cet algorithme pour implémenter un circuit de test de

mémoire BIST pour détecter toutes les fautes de voisinage.

Index Terms—Algorithme March, BIST, NPSF, Test de

memories.

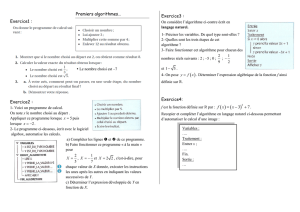

I. INTRODUCTION

Le model de NPSFs est important spécialement pour le test

de mémoires DRAM puisqu’il donne un meilleur taux de

couverture pour ce sort de mémoire [2]. NPSF exige un temps

de test long (plus de 100N opérations de lecture/écriture) où N

est le nombre de cellules dans la mémoire. Quelques

approximations ont été proposées pour détecter NPSFs tel

comme la méthode de “tiling” [3], [4], de deux groups [5], [6]

algorithmes de row-March [7] et de multiples backgrounds

[8], [9]. Les trois premières méthodes ont de différents

inconvénients tel comme un bas taux de couverture et un

temps de test très long. Les algorithmes de March

traditionnelles sont souvent utilisés pour le test de mémoire

car ils ont un caractéristique de complexité de temps linéal, ils

présente un taux de couverture haut et ils sont aussi faciles à

implémenter en utilisant BIST. Le problème avec les

algorithmes MARCH traditionnel est qu’il ne détecte pas tous

les NPFS, cependant, ils peuvent être modifié en utilisant

background de donnée multiple pour générer tous le patterns

de voisinage.

Ce document décrive l’implémentation d’un circuit de test

pour tester toutes les NPSF d’un mémoire en utilisant BIST.

Pour ce faire nous nous avons basé sur la méthode de

détection de fautes de voisinages à backgrounds multiples

proposés par K. Cheng, M. Tsai et C. Wu [1]. Cette méthode

détecte toutes les NPSF statiques, NPFS passifs et NPFS

actifs. Additionnellement le temps de test est plus court, le

taux de couverture est complet pour tous les NPSF et

l’implémentation BIST est facile.

II. MODEL DE FAUTES

Un “Neighborhood Pattern sensitive fault” est un faut de

couplage de multi-cellule. Il arrive lorsque le contenu d’une

cellule de la mémoire ou la capacité de changement de la

cellule est influencé par certain pattern d’autres cellules

voisines dans la mémoire. En général la cellule couplée est

appelé “base” et les cellules de couplage sont appelés

“deleted neighborhood cells”. Le NPSF à 5 cellules (NPSF-1)

est montre dans la Fig. 1.

Fig. 1. NPSF à 5 cellules (NPSF-1) [1].

Le voisinage inclut la cellule de base et les cellules de

voisinage effacées (les cellules N,E,W,S sont physiquement

adjacent à B). Ce model de faute est catégorisé dans trois sub-

types de fautes [4].

1) NPFS Statique (SNPSF): Il arrive si la cellule de base

est forcé à certain état en raison de l’apparition de certain

pattern dans les cellules voisines. Pour détecter les SNPSF,

tous les 32 patterns de voisinage statique montré dans la Table

I(a) doivent être appliqués.

2) NPFS Passive (PNPSF): Il arrive si la cellule de base ne

peut pas changer de l’état 0 à 1 ou 1 à 0 en raison de

l’apparition de certain pattern dans les cellules voisines. Pour

détecter les PNPSF, tous les 32 patterns de voisinage passif

montré dans la Table I(b) doivent être appliqués.

Algorithme de Test de Mémoire pour

"Neighborhood Pattern sensitive Faults"

Andrey Gonzalez, Negin Sahraii

2

3) NPFS Active (ANPSF): Il arrive si la cellule de base est

forcé à certain état lorsque un transition arrive dans un seule

cellule voisine tandis les autres cellules voisines prendre un

certain pattern. Pour détecter les ANPSF, tous les 128 patterns

de voisinage actif montré dans la Table I(c) doivent être

appliqués.

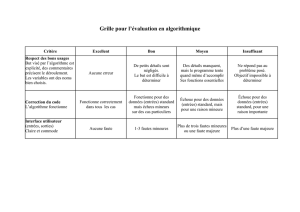

Table I.

Neighborhood patterns [4]

III. ALGORITHME MARCH

Les algorithmes March traditionnelles couvrent seulement

un petit pourcentage des NPSFs. Dans un élément March

typique lorsque on lit ou écrit la cellule base (B), toutes le

cellules avec adresse plus haute que B ont le même état. La

même chose arrive avec les cellules avec adresse plus basse

que B. Par exemple, quand un élément March ⇑(R0,W1) est

appliqué, toutes les cellules avec adresse plus haute que B

seront dans l’état 0. Les cellules avec adresse plus basse que B

seront dans l’état 1. Le quatre possibles état de la mémoire

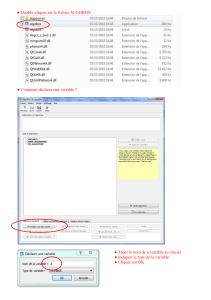

complet est montré dans la Fig. 2.

Fig. 2. Quatre états possibles de la mémoire en utilisant des

éléments March conventionnel sur un background solide

[1].

La majeure partie des NPSFs ne peut pas être activé par le

test March conventionnel. Le taux de couverture est plus petit

que 30% si l’algorithme March utilise seulement backgrounds

de données solides. Si on utilise backgrounds de données

multiples, tous les patterns de voisinage peuvent être générés

[8], [9]. La Fig. 3. montre quatre états de mémoire possibles

en utilisant le même élément March avec un autre

background.

Fig. 3. Quatre états possibles de la mémoire en utilisant des

éléments March conventionnel sur un background multiple

[1].

Dans la Fig. 3. “a” est le contenu de la cellule et “b” est le

complément de cet valeur. Différents backgrounds de données

multiples généreront différents patterns de voisinages. Pour

détecter toutes les fautes de voisinage on doit utiliser huit

backgrounds multiples et l’algorithme March-12N proposé en

[1]. Il détecte tous les NPSFs avec un temps de test de 96N

(12x8N) où 12 est égal au nombre des opérations March et 8

le nombre de backgrounds à utiliser. L’algorithme est le

suivant :

(ra)}.

wa);(rb, wb);wa,(rb, wb);ra,( wa);wb,(ra, (wa); {

⇑

⇑⇑⇑⇑c

Le première élément March (wa)) (cdans l’algorithme

précédente initialise la mémoire avec le background

correspondant. Les backgrounds de données multiples sont

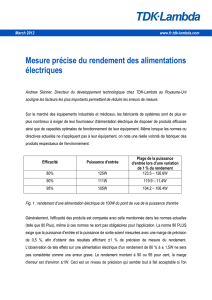

montrés dans la Fig. 4. Dans cette figure on peut remarquer

que le background bit “a” est généré en utilisant l’adresse de

lignes et de colonne de la mémoire. Cette méthode de

génération de background est avantageuse puisque on peut

savoir la valeur du bit qui a été écrit dans la mémoire

(initialisation) pour le comparer dans une opération de lecture

March.

3

Fig. 4. Huit backgrounds avec ses équations de génération

de background [1].

L’algorithme March-12N ne couvre pas les fautes de

adressage et toutes le fautes de couplage. Si on veut couvrir

les fautes AF et CFst, on ajoute 4N opérations à MARCH-12

seulement pour le background 1. Donc le background 1

prolongé à 16N opérations est le suivant :

(ra)}. wa);(rb,wb);(ra,

wa);(rb, wb);wa,(rb, wb);ra,( wa);wb,(ra, (wa); {

c

c

⇓⇓

⇑⇑⇑⇑

Toutes les fautes de mémoire sont couvertes avec cet

algorithme “extended 12N March”. L’algorithme résultant a

un temps de test de 100N (16N + 12x7N).

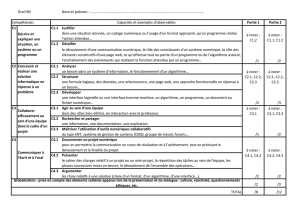

IV. IMPLEMENTATION BIST

L’implémentation du circuit de test est base sur l’algorithme

12N-March prolongé. Comme on a expliqué dans la section

précédente, pour trouver les fautes de voisinages dans une

RAM, on utilise la méthode March et de backgrounds

multiples ensemble. L’implémentation du circuit BIST est

montrée dans la Fig. 5. La description de chaque parti du

circuit est la suivante:

1) Contrôleur BIST: La Fig. 6. montre une machine à état

qui exécute les opérations des éléments March. Comme on

veut exécuter les éléments de March avec 8 différents

backgrounds on traverse les états de la machine 8 foies. Dans

les états “wa” et “wb”, le pulse “wr_n” de RAM la rends active

dans le mode écriture. La donnée “a” ou “b”, qui est fournit

par le générateur de background, est écrit dans l’adresse

correspondant de la RAM. Dans les états “rb” et “wb”, le pulse

“oe_n” de RAM la rends active dans le mode lecture et la

donnée correspondant de RAM est mit sur le bus “data”. En

même temps la donnée prévu (a ou b) est comparé avec la

donnée en provenant de la RAM par “comparator”. Si ils ne

sont pas égaux, le signal erreur se rend active et le contrôleur

BIST se rend à l qui correspond à l’état erreur. On a aussi

définit un signal de sortie dans la machine à état “datain” qui

permet configurer le générateur de background pour

différencier le sorte de bit généré par le générateur : “a” ou “b”

(a : datain =0, b : datain=1).

RAM

Buffe

r

Comparator

Ram Pulse

Generator

UP/Down

Counter

Background

pattern Generator

BIST Controller

(State machin)

Datain

writ

clea

r

count

lastadd

firstadd

fina

error

countu

p

add(0-14)

test

wr_n

oe_n

cs

write

datab data

add0

,

add1

,

add6

315

oe_n

rst_n

clk

rst_n

bgf

bgc

test

s

y

serror

s

y

scorrect

test

clk

Fig. 5. Implémentation du circuit BIST.

{

↨

(

wa

)

; ↑

(

ra,w

b

,wa

)

; ↑

(

ra,w

b)

; ↑

(

r

b

,wa,w

b)

; ↑

(

r

b

,wa

)

; ↓

(

ra,w

b)

;↓

(

r

b

,wa

)

;

↨

(

ra

)}

.

Algorithme March 16-N

m0 m1 m2 m3 m4 m5 m6 m7

start m0

waa

m0

wa m1

ra m1

wa

m1

wb m1

wbb

m1

raa m1

waa

m2

raa m2

ra

m2

wb

m3

wa

m2

wbb

m3

rbb

m3

waa

m3

wbb m3

wb m3

rb

m4

waa m4

rbb m4

rb

m4

wa

m5

ra

m5

wb

m5

raa

m5

wbb

m6

rb

m6

wa

m6

waa m6

rbb

m7

ra

m7

raa

correct

error

test=0

test=1

lastadd=0

bgc=1

last

add=1

lastadd=0

last

add=1

last

add=1

last

add=1

last

add=1 lastadd=0

lastadd=0

lastadd=0

lastadd=0

last

add=1

error=1

first

add=1 firstadd=0

firstadd=0

first

add=1

error=1

error=1

error=1

error=1

error=1

bgc=0

bgf=1

bgf=0

s0 s6 s8

s10

s3s1 s2

s9

s7

s4 s5

s13

s11

s12

s14

s15

s19

s20s21

s18 s17 s16

s23

s24

s22

s25s26

s30 s29 s27

s34

s28

s31

s32s33

Fig. 6. Machine à état qui exécute les opérations des

éléments March.

2) Générateur de Background: Il fournit le bit de

background “a” ou son complément “b” basée sur la valeur de

“datain”. On sait que la donnée de background dépend du bit0

et du bit1 de l’adresse de “column” et que il dépend aussi du

bit0 de l’adresse de “row” comme est montré dans la Fig. 4.

Dans la RAM utilisée, add15….add6 correspond à l’adresse

de “row” et add5….add0 correspond a l’adresse de “column”.

Donc la sortie de “background generator” dépend de “add0”,

“add1”, “add6” et “datain”.

4

Il y a un compteur (de 1 jusque 8) dans le générateur de

background qui définit le numéro de background à utiliser.

Dans le cas de BG1 le signal “bgc” se rend actif et dans le cas

de BG8, le signal “bgf’” se rend actif. Dans le dernier état de

l’algorithme, un signal “fina” est envoyé à “background

generator” et le compteur qui est dans le générateur de

background s’incrémente en une unité pour pouvoir ainsi

travailler avec la prochain background. Dans le dernier état de

l’algorithme le signal “bgf” est vérifié. Si on travaille avec le

BG8 (bgf actif), la machine à état termine le test et il se rend à

l’état ‘correct’.

Comme on a expliqué dans la section précédente

l’algorithme March 16-N est utilisé pour tester le BG1. Pour

les autres BG, on utilise March 12-N (il ne exécute pas les

éléments m5 et m6). Donc dans la machine à état, à la fin de

m4 on vérifie le signal “bgc”. Si “bgc” est actif, on passe à

l’état suivant qui correspond à m5, sinon il se rend au premier

état de m7.

3) Compteur: C’est utilisé pour fournir, incrémenter,

décrémenter les adresses nécessaires pour l’exécution de les

éléments March dans la RAM.

4) Buffer à trois états: Pendent le processus d’écriture, il

permet que la sortie du générateur de background soit mit sur

le bus “data ” de la RAM.

5) Générateur de pulse de RAM: Il fournit les signaux “cs”,

“oe_n” et “wr_n” à la RAM pour contrôler les opérations

March de lecture et écriture de la mémoire.

La table II montre tous les signaux utilisés dans le circuit

BIST et sa signification.

Table II.

Signaux circuit BIST

Signal

test

error

fina

bgf

bgc

datain

firstadd

lastadd

countup

count

clear Si '1', 'counter' recommence la compte (première adresse de mémoire)

write

syserror

syscorrect

datab

cs

oe_n

wr_n

signification

BG2 et les états(wa ou ra) : add6+add0 BG2 et les états(wb ou rb): not(add6+add0)

BG7 et les états(wa ou ra): add0+add1 BG7 et les états(wb ou rb): not(add0+add1)

Si '1', 'counter' compte

Dans le dernier état de l'algorithme pour chaque Background, il devient '1'

Pendent les états wa et ra, il devient '0' et pendent les états wb et rb, il devient '1'

Si '1', pulse we_n actif, si '0', pulse oe_n actif

BG6 et les états(wa ou ra): add1+add6 BG1 et les états(wb ou rb):not(add1+add6)

si test=0 : oe_n='Z', si test=1 et write=0 : oe_n=not(clk), si test=1 et write=1 :oe_n='1'

si test=0 : wr_n='Z', si test=1 et write=1 : wr_n=not(clk), si test=1 et write=0 :wr_n='1'

si '1' le contrôleur BIST commence à tester la RAM

si datab#data et oe_n ='0' ,error= '1' ,sinon error= '0'

Quand background=1, bgc= '1'

Quand background=8, bgf = '1'

Quand add="000000000000001",il devient 1

Quand add="111111111111110",il devient 1

BG3 et les états(wa ou ra): add6 BG1 et les états(wb ou rb): not add6

BG5 et les états(wa ou ra): add1 BG5 et les états(wb ou rb): not add1

BG4 et les états(wa ou ra): add0 BG4 et les états(wb ou rb): not add0

BG8 et les états(wa ou ra):add6+add0+add1 BG8 et états(wb ou rb):not(add6+add0+add1)

Si test=1 :cs= '0', sinon :cs=' Z'

Quand une erreur est détecte, syserror= '1'

Quand le processus de l'algorithme termine sans erreur, syscorrect= '1'

BG1 et les états(wa ou ra): '0' BG1 et les états(wb ou rb): '1'

Si '1', 'counter' incrémente l'adresse, sinon 'counter' décrémente l'adresse

V. RESULTATS DE LA SIMULATION DU CIRCUIT BIST

On a décrit le circuit de BIST en utilisant codes VHDL. La

simulation du test a été fait sur un modèle de RAM normal et

des modèles de RAM défectueuses. On a considéré une RAM

avec une capacité de (32k x 1bit) qui contient 64 “column” et

512 “row”. Ce RAM est montré dans la Fig. 7.

Pour pouvoir simuler des RAMs défectueuses, on a ajouté

les modèles de faute voisinage passif, actif et statique dans le

modèle VHDL de la RAM. Pour manipuler les cellules de

voisinage on a établi que l’adresse de la cellule défectueuse

est “addbase”, les adresses des cellules voisines sont :

adresse(N)=addbase-64, adresse(W) =addbase-1, adresse(E)=

addbase+1, adresse(S)=addbase+64.

Fig. 7. Model de mémoire utilisé dans la simulation.

Dans le résultat de simulation sur le model de RAM normal,

on observe que le contrôleur de BIST (la machine à état)

traverse tous les états par tous les 8 backgrounds et à la fin, il

arrive à l’état 33(état correct) et le signal “syscorrect” se rend

active.

Dans les résultats de simulation du test sur les modèles de

RAMs défectueuses, on observe que le contrôleur BIST

détecte tous les types de fautes de voisinages tels comme les

fautes statiques, passifs et actifs sur les adresses de cellules

défectueuses. L’algorithme March 12-N prolongé a aussi la

capacité de détecter les fautes de adressage et tous les fautes

de couplage.

Le temps total du test est de 100N, où N est le nombre de

cellules dans la mémoire. Dans le cas de notre mémoire de

32Kbits le temps de test a été 640ms en utilisant une horloge à

5 Mhz.

VI. CONCLUSION

On a proposé un algorithme March à backgrounds multiples

qui nos permet détecter les fautes de voisinage NPSF statique,

passif et actif dans un mémoire semi-conducteur.

Additionnellement cet algorithme détecte aussi des autres

fautes tels comme SAF, TF, AF, SOF et CF. L’algorithme

MARCH 12-N prolongé en utilisant 8 backgrounds multiples

peut détecter toutes les fautes précédemment mentionnées

avec un temps de test de 100N. On a implémenté un circuit de

test de mémoire BIST pour faire le test. Les résultats de

simulation du circuit de test nous indiquent que la méthode

proposée est effective pour détecter toutes les fautes de

voisinage. Un Algorithme de diagnostic peut être implémenté

pour détecter le type et l’endroit de la faute détecté en utilisant

dictionnaires de fautes qui contiennent signatures March. Si

deux fautes ont dictionnaires de fautes différents on peut

distinguer le deux fautes.

5

REFERENCES

[1] K. Cheng, M. Tsai, C. Wu, “Efficient Neighborhood Pattern-Sensitive

Fault Test Algorithms for semiconductor memories” proceedings of the

19th IEEE VLSI Test Symposium (VTS’01).

[2] M. Bushnell, V. Agrawal. “ Essentials of Electronic Testing”, Ed.

Kluwer Academic Publishers, 2000, pp. 532-534.

[3] J. P. Hayes, “Testing memories for single-cell pattern sensitive

fault”, IEEE Transactions on Computers, vol. 29, no. 2, pp. 249–254,

Mar. 1980.

[4] A. J. van de Goor, Testing Semiconductor Memories: Theory and

Practice, JohnWiley & Sons, Chichester, England, 1991.

[5] D. S. Suk and S. M. Reddy, “Test procedures for a class of pattern-

sensitive faults in semiconductor random-access memories”, IEEE

Transactions on Computers, vol. 29, no. 6, pp. 419–429, June 1980.

[6] K. K. Saluja and K. Kinoshita, “Test pattern generation for API faults in

RAM”, IEEE Transactions on Computers, vol. 34, no. 3, pp. 284–287,

Mar. 1985.

[7] M. Franklin and K. K. Saluja, “Testing reconfigured RAM’s and

scrambled address RAM’s for pattern sensitive faults”, IEEE

Transactions on Computer-Aided Design of Integrated Circuits, vol. 15,

no. 9, pp. 1081–1087, Sept. 1996.

[8] B. F. Cockburn, “Deterministic tests for detecting scrambled pattern-

sensitive faults in RAMs”, in Proc. IEEE Int. Workshop on Memory

Technology, Design and Testing (MTDT), 1995, pp. 117–122.

[9] V. Yarmolik, Y. Klimets, and S. Demidenko, “March PS(23N) test for

DRAM pattern-sensitive faults”, in Proc. Seventh IEEE Asian Test

Symp. (ATS), Singapore, Dec. 1998, pp. 354–357.

1

/

5

100%