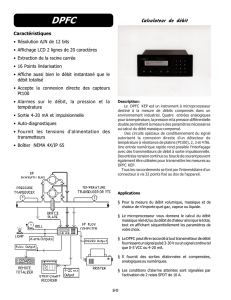

TP4 : Technologie des composants I

RIGLET Aurélie MIQ 3

& ROGNON Vincent Pour le 17/01/2007

TP4 : Technologie des composants

I- Etude expérimentale : famille TTL

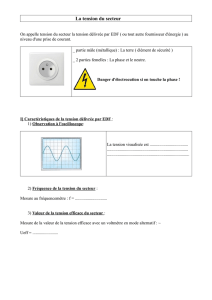

1. Caractéristiques de transfert Vo(Vi)

On remarque que pour la tension Vo mesurée, la zone de niveau bruité se situe entre

1.4V et 1.6V. Alors que pour les valeurs ‘constructeur’ indiquent entre 0.8V et 2V. Ceci

permet au constructeur de se donner une marge par rapport à ses clients, d’autant plus que

chaque composant est unique et que cette plage va donc varier.

Vi (en Volts) Vo (en Volts)

0 4

0,25 4

0,5 4

0,75 4

0,8 4

1 4

1,25 4

1,3 3

1,4 2,4

1,5 1

1,6 0

2 0

3 0

4 0

5 0

Gabarit du diagramme Vo(Vi)

-1

0

1

2

3

4

5

0123456

Vi (en Volts)

Vo (en Volts)

V0,mesuré

Vo,constructeur

Fig. 1: Evolution de la tension de sortie en fonction de celle d'entrée

Electronique Numérique -TP2- Nov.06

2

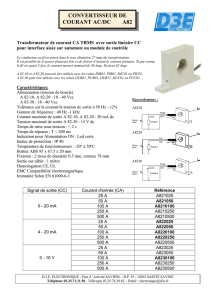

2. Caractéristiques de Sortie Vo=f(Io)

Montage à réaliser si l’on est à l’état haut (le courant est sortant) :

Calcul de Rmin pour ne pas détruire la porte logique :

Au niveau ‘haut’, on à l’équation : IOH= 3

50.4.10

OH U

I

A

RR −

==< d’où :

min 3

512500

0.4.10

R−

>=Ω. En pratique nous avons aux bornes de notre résistance : 12 300

Ω

.

Ce qui donne le graphique suivant :

Vo (en Volts) Vr (en Volts) Io=Vr/12300 (en mA)

3.5 3.4 0.27

3.5 3.2 0.26

3.6 3 0.24

3.6 2.6 0.21

3.6 2.2 0.18

3.6 2 0.16

3.7 1.5 0.12

3.9 1 0.08

4 0.75 0.06

4 0.5 0.04

4.1 0.4 0.03

Tableau 1 : Relevé des valeurs Vo en fonction de Io

V1=0V

1

V

V0=4,4V

IOH

VR

Fig. 2: Evolution de la tension de sortie en fonction du courant de sortie à l'état haut

Vo=f(Io)

3.4

3.5

3.6

3.7

3.8

3.9

4

4.1

4.2

00.10.20.3

Io en mA

Vo en Volts

Vo=f(Io)

Electronique Numérique -TP2- Nov.06

3

On remarque que la tension diminue quand l’intensité du courant augmente.

Montage à réaliser si l’on est à l’état bas (le courant est entrant dans la porte) :

Tableau 2 : Relevé des tensions et du courant en sortie de la porte

Vo (enVolts) Vr (enVolts) Io (en mA)

0.28 4.71 7.6

0.26 3.9 6.3

0.25 3.5 5.6

0.23 3 4.8

0.22 2.5 4

0.2 2 3.2

0.19 1.5 2.4

0.17 1 1.6

0.16 0.75 1.2

0.15 0.5 0.8

0.14 0.25 0.4

V1=5V

1

V

V0=0V

IOL

VR

5V

Vo=f(Io)

0

0.05

0.1

0.15

0.2

0.25

0.3

02468

Io (en mA)

Vo (en Volts)

Vo=f(Io)

Fig.3: Evolution de la tension de sortie en fonction du courant de sortie à l'état bas

Electronique Numérique -TP2- Nov.06

4

On remarque la tension augmente quand l’intensité du courant augmente.

3. Mesure des temps de propagation

Pour pouvoir réaliser la mesure du temps de propagation, nous avons effectué le montage

suivant :

Et nous avons obtenu comme mesure, 9, 4tns

Δ

=(compris entre 2ns et 11ns d’après le

constructeur).

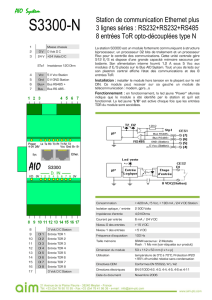

II- Etude expérimentale : famille CMOS

Vi (enVolts) Vo (enVolts)

0.1 5

1 5

1.5 5

2 5

2.7 5

2.8 Bruit

3 0

4 0

5 0

Tableau 3: Relevé de la tension de sortie en fonction de la tension d'entrée

1

1

1

CLK

1

2

Vo=f(Vi)

0

1

2

3

4

5

6

0246

Vi (en Volts)

Vo (en Volt

Vo mesurés

Vo constructeurs

Electronique Numérique -TP2- Nov.06

5

On remarque que pour la tension Vo mesurée, la zone de niveau bruité se situe autour

de 2.8V. Alors que pour les valeurs ‘constructeur’ indiquent entre 1.5V et 3,5V. Ceci permet

au constructeur de se donner une marge par rapport à ses clients, d’autant plus que chaque

composant est unique et que cette plage va donc varier.

On remarque que la zone incertaine du composant est plus petite qu’en technologie TTL. La

plage, ic,i est large de 0.1V (au niveau de 2.8V en entrée).

2. Mesure des temps de propagation

Nous avons effectué le même montage qu’en TTL et nous avons obtenu un temps de

propagation 68tnsΔ= (compris entre 60ns et 125ns d’après le constructeur).

III- Comparaison des deux familles

D’après les résultats obtenus, il apparaît que la famille CMOS offre une plage de

niveau bruité moins importante qu’en technologie TTL. De plus, les valeurs de tension sont

plus stables en famille CMOS, 5V à l’état haut et 0V à l’état bas, alors qu’en TTL à l’état

haut, Vo varie entre 4.4 Volts et 3.8 Volts.

Néanmoins, la famille TTL apporte des temps de propagations nettement moins important

qu’en CMOS.

IV- Interfaçage de composants :

Ce montage ne pourra pas fonctionner. En effet, il y a nécessité, pour les composants 74LS05

à collecteurs ouverts, d’une résistance de pull up afin d’imposer l’état logique ‘haut’.

Fig.4:Evolution de la tension de sortie en fonction de celle d'entrée

6

6

7

7

8

8

1

/

8

100%