Methodologie de conception des protections des circuits intégrés

Methodologie de conception des protections des circuits

int´egr´es contre les d´echarges ´electostatiques

Nicolas Nolhier

To cite this version:

Nicolas Nolhier. Methodologie de conception des protections des circuits int´egr´es contre

les d´echarges ´electostatiques. Micro et nanotechnologies/Micro´electronique. Universit´e Paul

Sabatier - Toulouse III, 2005.

HAL Id: tel-00265344

https://tel.archives-ouvertes.fr/tel-00265344

Submitted on 19 Mar 2008

HAL is a multi-disciplinary open access

archive for the deposit and dissemination of sci-

entific research documents, whether they are pub-

lished or not. The documents may come from

teaching and research institutions in France or

abroad, or from public or private research centers.

L’archive ouverte pluridisciplinaire HAL, est

destin´ee au d´epˆot et `a la diffusion de documents

scientifiques de niveau recherche, publi´es ou non,

´emanant des ´etablissements d’enseignement et de

recherche fran¸cais ou ´etrangers, des laboratoires

publics ou priv´es.

Synthèse de travaux

Préparée au :

Laboratoire d'Analyse et d'Architectures des Systèmes du CNRS

En vue de l'obtention de l'Habilitation à Diriger des Recherches de

l'Université Paul Sabatier de Toulouse

Spécialité : Electronique, Optronique et Systèmes

Par :

Nicolas NOLHIER

Docteur de l'INSA de Toulouse

Maître de Conférences

Méthodologie de conception des protections des circuits

intégrés contre les décharges électrostatiques

Soutenue le 30 Novembre 2005 au LAAS/CNRS

Composition du jury :

Président L.ESCOTTE Professeur à l'Université de Toulouse III

Rapporteurs O.BONNAUD Professeur à l'Université de Rennes I

D.LEWIS Professeur à l'Université de Bordeaux I

R.VELAZCO Directeur de Recherche au CNRS

Directrice M.BAFLEUR Directrice de Recherche au CNRS

Examinateur C.HUET Ingénieur Airbus

G. MENEGHESSO Professeur à l'Université de Padova, Italie

Invité P. RENAUD Ingénieur Freescale

Résumé :

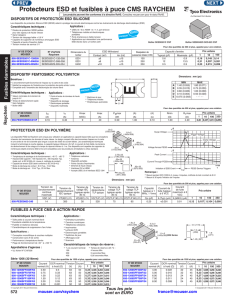

La problématique des agressions par décharges électrostatiques (ESD) est un facteur critique

dans la fiabilité des circuits intégrés. Ce document effectue la synthèse des travaux menés au

LAAS-CNRS dans ce domaine. Les points suivants seront plus particulièrement abordés :

- L’étude des mécanismes physiques qui gèrent le comportement d’un composant lors d’une

décharge ESD

- La mise en place d’une méthodologie de conception de structures de protection

- Son application au développement de solutions de protection innovantes

La dernière partie de ce document propose les perspectives de cet axe de recherche qui sont

principalement motivés par les progrès technologiques des circuits intégrés, l’évolution des

normes de robustesse et l’extension de nos travaux au niveau du système.

Mots-clés :

Décharges électrostatiques, ESD, protections ESD, TLP, Régimes fortes injections.

Abstract :

Electrostatic Discharge (ESD) stresses strongly impact on integrated circuits reliability. The

research work led in LAAS-CNRS laboratory on this field is synthesized in this document.

The following topics are detailed :

- physical mechanisms study of device behavior during an ESD stress

- design methodology for ESD protection devices

- novelty ESD protections development

The final part of this report presents an outlook which is closely tied to integrated circuits

technology advance, ESD standard development and system level approach.

Keywords :

ElectroStatic Discharges, ESD, ESD protections, TLP, very high current injection.

A Isabelle,

Adrien et Raphaël

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

1

/

98

100%