Une architecture unifiée pour la divergence de contrôle et la

Une architecture unifiée pour la

divergence de contrôle et la

divergence mémoire en SIMT

Sylvain Collange

Arénaire, LIP, ENS de Lyon

SympA'14

11 mai 2011

Hier (2000-2010)

Multi-cœurs homogènes

GPU CPU

multi-cœur GPU

Cœurs

optimisés

latence

Aujourd'hui (2011-...)

Intégration CPU+GPU sur puce

Intel Sandy Bridge

AMD Fusion

Projet NVIDIA Denver/Maxwell

Demain

multi-cœurs hétérogènes

Différence entre GPU et cœurs

optimisés débit?

Comment franchir ce pas? Multi-cœur hétérogène

Cœurs

optimisés

débit

?

Architecture SIMT

Modèle de GPU

Gestion de la divergence : solutions existantes

Gérer la divergence par PC multiples

Motivation

Politique d'ordonnancement

Proposition d'architecture

Unité d'arbitrage

Fusion avec l'unité mémoire

Résultats

Logiciel

Matériel

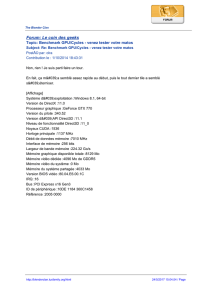

Architecture : modèle de programmation multi-thread (SPMD)

Microarchitecture SIMT

Single Instruction, Multiple Threads

Chemins de données en matériel : unités d'exécution SIMD

!"#

Simplification,

sans perte de généralité

1 séquenceur d'instructions

n Processing Elements (PE)

PE débrayables individuellement

Pas de pipeline

1 PE = 1 thread

PE 1 PE 2

Architecture SIMT primitive. Musée Gallo-

Romain de St-Romain-en-Gal, Vienne

1 instruction PE 0 PE 3

Thread 0 Thread 1 Thread 2 Thread 3

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

1

/

24

100%