Que faut il retenir?

Réalisé par :

Encadré par : MR TANARI

Introduction :

La définition d’un processeur

Caractéristique technique

CPU + mémoire

Les types de processeurs

RISC Vs. CISC

Comparaison

Microcontrôleur

Que faut il retenir?

La définition d’un processeur

C'est la pièce maîtresse de l'ordinateur. Elle

est ce que le cerveau est à l'homme pour

l'ordinateur. Son but est de contrôler et de

traiter l'ensemble des requêtes émises par

l'utilisateur ou par les pièces de

l'ordinateur afin que chacune puisse

exécuter sa tâche lorsque nécessaire.

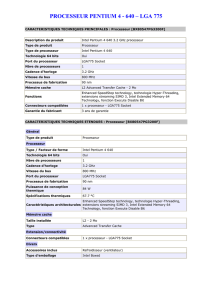

Caractéristique technique

La fréquence

elle permet de comparer facilement 2 processeurs. Mais attention de ne pas comparer

l’incomparable .

Par exemple, un Pentium 4 à 3.2 GHz sera moins performant qu'un Core 2 Duo à

2Ghz.

Le cache

Le cache est une mémoire pour les calculs qui reviennent souvent. Cette mémoire est

beaucoup plus rapide que la RAM, et influe donc sensiblement sur les

performances globales du CPU.

Le socket

reçoit le processeur, les sockets ont un nombre différent de « contact » afin de

recevoir les picots du processeur. Ce nombre correspond au nom du socket (socket

AM2,AM2+,AM3,775,1156 etc..).

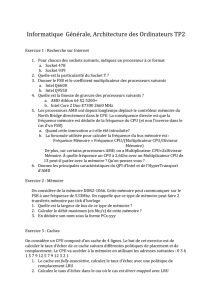

CPU + mémoire

Memory PC

address Bus

Data Bus IR

ADD r5,r1,r3

200 200

ADD r5,r1,r3

Instruction fetch

PC

CPU

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

1

/

15

100%