Diapositive 1 - E

Generalites

Présentation

Exemples de système

Régulation de débit,

CD audio numérique,

Etc.

Signal analogique

provenant du

monde extérieur.

Par exemple :

-tension issue d'un

capteur de

température

-- tension issue

d'un capteur

d'humidité

-etc.

Signal analogique

provenant du

monde extérieur.

Par exemple :

-tension issue d'un

capteur de

température

-- tension issue

d'un capteur

d'humidité

-etc.

Cette fonction

transforme

(convertie) la tension

analogique Ve en

signal numérique sur

N bits

Signal analogique

provenant du

monde extérieur.

Par exemple :

-tension issue d'un

capteur de

température

-- tension issue d'un

capteur d'humidité

-etc.

Cette fonction

transforme (convertie)

la tension analogique

Ve en signal

numérique sur N bits

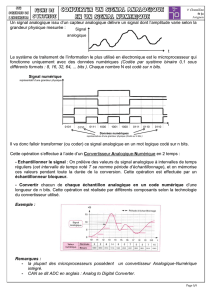

Le système de traitement numérique

assure le traitement numérique de

l'information.

Ce système est en général constitué

D'un microprocesseur

Ou

D'un microcontrôleur

Signal analogique

provenant du

monde extérieur.

Par exemple :

-tension issue d'un

capteur de

température

-- tension issue

d'un capteur

d'humidité

-etc.

Cette fonction

transforme (convertie)

la tension analogique

Ve en signal numérique

sur N bits

Le système de traitement numérique

assure le traitement numérique de

l'information.

Ce système est en général constitué

D'un microprocesseur

Ou

D'un microcontrôleur

Cette fonction

transforme

(convertie) le signal

numérique de M bits

en provenance du

microprocesseur en

une tension ou un

courant analogique.

Signal analogique

provenant du

monde extérieur.

Par exemple :

-tension issue d'un

capteur de

température

-- tension issue d'un

capteur d'humidité

-etc.

Cette fonction

transforme (convertie)

la tension analogique

Ve en signal numérique

sur N bits

Le système de traitement numérique

assure le traitement numérique de

l'information.

Ce système est en général constitué

D'un microprocesseur

Ou

D'un microcontrôleur

Cette fonction

transforme

(convertie) le signal

numérique de M bits

en provenance du

microprocesseur en

une tension ou un

courant analogique.

signal

analogique, qui

peut commander :

- un moteur à

courant continu

- une

électrovanne

-etc.

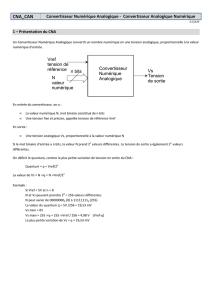

CONVERTISSEURS Numérique Analogique (CNA) / Analogique Numérique (CAN)

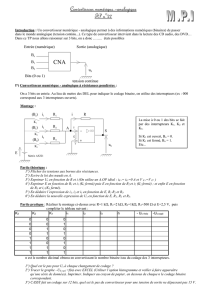

Symbolisation

Système

de traitement

numérique

Ve Vs

N bits

de sortie M bits

d'entrée

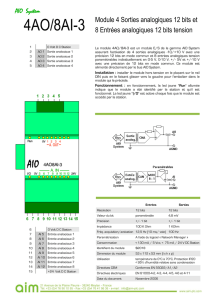

Ce type de CNA n’utilise que deux valeurs de résistances. La figure donne un exemple de ce

type de convertisseur à 4 bits.

Les commutateurs sont commandés par le code numérique. La valeur analogique est la somme

des courants aboutissant à l’entrée "-"de l’amplificateur opérationnel

CONVERTISSEUR A RÉSEAU R/2R

Chaque commutateur (k0, k1, k2, k 3) peut être relié à la masse (position " 0 "), soit à la

tension Ve (position " 1 ").

On montre aisément que la résistance interne de ce réseau est R. En effet, si on

suppose que tous les commutateurs sont à la masse, la résistance équivalente entre la

sortie et la masse est R

Analyse du montage

Ce résultat est également valable quelque soit la position de (k0, k1, k2, k 3) si la résistance

interne du générateur Ve est faible devant R.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

1

/

33

100%