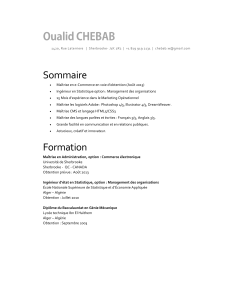

Multiprocesseurs - Université de Sherbrooke

Gei 431

Architecture des ordinateurs II –Frédéric Mailhot

Les multiprocesseurs

Jusqu’à maintenant, nous avons parlé longuement

des microprocesseurs.

Nous allons maintenant étudier les

multiprocesseurs, comment ils fonctionnent,

quels sont les problèmes particuliers qui

apparaissent.

© 2001 Frédéric Mailhot Université de Sherbrooke

Les multiprocsseurs

Les multiprocesseurs

•Périodiquement, depuis les années ’60, on a prédit la fin

des uniprocesseurs, au profit des multiprocesseurs

•On parle souvent de la vitesse de la lumière comme d’une

limite proche d’être atteinte:

C = 3 X 10 ^ 8 m/s –» 15 cm / 0,5 ns (2 GHz)

On dit que des architectures nouvelles (multiprocesseurs)

devront être utilisées pour continuer d’améliorer la

performance

•Mais… depuis 1985, l’augmentation de performance des

processeurs est la plus importante depuis la fin des années

’50!

© 2001 Frédéric Mailhot Université de Sherbrooke

Les multiprocsseurs

Les multiprocesseurs –pourquoi

•En supposant que les microprocesseurs demeurent la

technologie dominante pour les uniprocesseurs, il semble

naturel d’imaginer en connecter plusieurs ensemble pour

augmenter la performance

•Il n’est pas clair que le taux d’innovation au niveau de

l’architecture pourra se continuer longtemps

•Il semble qu’il y ait des progrès constants dans les 2

domaines où les machines parallèles ont le plus de

difficulté: le logiciel et les interconnexions

© 2001 Frédéric Mailhot Université de Sherbrooke

Les multiprocsseurs

Les types de multiprocesseurs

•Taxonomie proposée par Flynn dans les années

’60:

SISD (Single Instruction Single Data): uniprocesseur

SIMD (Single Instruction Multiple Data): plusieurs

processeurs, qui exécutent en parallèle les mêmes

instructions sur plusieurs données

MISD (Multiple Instruction Single Data): pas d’exemple

connu

MIMD (Multiple Instruction Multiple Data): plusieurs

processeurs qui opèrent de façon indépendantes ou

semi-indépendantes sur leurs données

© 2001 Frédéric Mailhot Université de Sherbrooke

Les multiprocsseurs

Types de multiprocesseurs utilisés

•Les premiers multiprocesseurs étaient du type

SIMD, et cette architecture est encore utilisée

pour certaines machines spécialisées

•Le type MIMD semble être la cible de choix de nos

jours pour des ordinateurs d’application

courante:

Les MIMD sont flexibles: on peut les utiliser comme

machines à un seul utilisateur, ou comme machines

multi-programmées

Les MIMD peuvent être bâties à partir de processeurs

existants

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

1

/

46

100%