33-Comment overclocker

Comment overclocker

AMD Athlon XP

Caractéristiques et overclocking

Introduction pour ceux qui découvrent

Le processeur AMD Athlon XP est actuellement l'un des plus répandus dans le marché de

l'informatique. Mais avec l'arrivée de l'architecture K8, l'Athlon XP (K7) arrive en fin de vie...

En revanche, on peut en conclure de par sa longévité que cette architecture en est arrivée à un

point extrêmement stable (le noyau du K8 est aussi pratiquement similaire à celui de K7), ce qui est très

bénéfique pour l'overclocking de ces processeurs, qui pour la plupart s'y prêtent volontiers... (Je traiterai

ici uniquement de l'Athlon XP)

Pour ceux qui ne connaissent pas ou peu ces procs, ceux qui commencent tout juste à arriver dans

le monde ou l'on achète plus sont PC chez e, grande surface, et qui commencent à s'intéresser au

hardware, nous allons d'abord commencer par voir comment est constitué ce processeur, voir toutes ses

caractéristiques, et voir aussi les différentes séries d'Athlon XP... (Bah oui, y'en a pas qu’un..). Ensuite, on

verra la méthode d'overclocking à appliquer pour faire évoluer les performances. Si vous savez déjà

overclocké, ce n’est pas la peine de lire cette page.

Tout d'abord, ceux qui arrivent dans notre merveilleux monde sont nombreux à se poser la

question "Pourquoi les AMD ont des fréquences plus basses que celle d'Intel, pour de mêmes

performances annoncées ??"

Ca, c'est la base, puisque c'est un problème d'architecture, que nous verrons un peu plus en détails.

La puissance d'un processeur doit se comparer au nombre de calculs effectués par secondes par le

processeur. Hors, les fréquences annoncées en MHz ne représentent que le nombre de cycles effectués par

le processeur en une seconde. C'est la que l'on en arrive à cette fameuse différence de fréquence. La

puissance du processeur se caractérise par un produit qui est:

IPC x Fréquence d'horloge = Performances.

L'IPC, c'est le nombre d'instructions traitées par cycle, et la fréquence d'horloge, c'est le nombre de

cycles traités par secondes. Les processeurs AMD calculent tous simplement plus d'instructions par cycles

que les processeurs Intel. C'est pour ca qu'AMD utilise des P-Rating pour qualifier ses processeurs, qui

eux sont déterminés en fonction du nombre de calcul effectués par le processeur.

C'est pour ca que l'on dit qu'un 3000+ est équivalent à un P IV 3 GHz. Ces 2 processeurs

exécutent approximativement le même nombre de calculs par secondes.

L'architecture de l'Athlon XP

Ce qui a fait la réputation de l'AMD Athlon XP, et qui fait que le nouveau K8 est très similaire du

K7, c'est tout simplement son architecture Quanti-Speed....

C'est cette architecture qui permet aux processeurs Athlon XP d'effectuer plus de calculs par cycle,

comme on vient de le voir plus haut.

Comme un peu de science ne fait de mal à personne, on va regarder cette architecture d'un peu

plus près.

Tous d'abord, voici ses principales caractéristiques. (Fonctionnement détaillé plus bas.)

o

Micro architecture superscalaire X86 Pipelinée avec neuf sorties

o

Décodeur d'instruction X86 à trois voies.

o

3 unités de calcul sur nombres entiers fonctionnant en mode pipeliné

o

3 unités de calcul d'adresse fonctionnant en mode pipeline

o

Fonctions évoluée d'anticipation des données

o

Tampons TLB

Voila pour les principales. Maintenant, on va regarder tout ca sur le schéma qui suit, et suivre les

explications du fonctionnement qui se trouvent en dessous. (Cliquez pour agrandir le shéma)

Fonctionnement de l'architecture Quanti-speed

L'extraction des instructions (fetch) s'effectue en étroite collaboration avec le cache L1 et le

mécanisme de prédiction des branchements. Si les données ne se trouvent pas dans le cache L1, alors le

proc va chercher dans son cache L2, ca qui est légèrement plus long. Par contre, si les données ne sont pas

dans le L2 non plus, alors c'est là que ca devient très long, puisqu'il faut accéder à la ram système.

Ces données sont ensuite apportées au décodeur X86 qui va convertir ces instructions en micro-

opérations (µOPs) de longueurs fixes. Le décodeur ayant 3 voies est donc capable de fournir 3 µOPs par

cycle.

A ce stade, on distingue les instructions simples qui se décodent en 2 µOPs maximum. Ces µOPs

sont donc "pacsés" pour être distribuées aux différentes unités de calcul par le biais de l'unité de contrôle

des instructions.

Les instructions complexes qui se décodent en plus de 2 µOPs sont décodées par la mémoire

interne. Ces instructions sont alors microcodées...

Les instructions se dirigent alors vers la partie ALU ou la partie FPU, par le biais du scheduler

(synchroniseur) respectif. C'est lui qui donne le rythme, qui régule le débit des instructions.

La partie ALU est celle qui traites les opérations simples en un cycle d'horloge, telles

que l'addition, rotation, décalage, opérations logiques (et, ou)....Elle est composée de 3 unités de calcul

entier et de trois unités d'adressage mémoire.

La partie FPU, c'est celle qui s'occupe de tous les calculs à virgule flottante (X87) telles que les

instructions MMX, 3DNow!, SSE et SSE2. Ces instructions nécessitent plus d'un cycle pour être

calculées...Ce sont principalement des instructions multimédia ! Le Fstore est la partie qui stock les

instructions calculées par le Fmul et le Fadd (Pipeline multiplicatrice et additionneuse).

Une fois que les instructions ont été calculées par les différentes unités de calcul, elles sont

récupérées par la cache L1, et sont ensuite expédiées vers le cache L2 si elles tardent à être rappelées et

quittent le processeur si elles ne sont pas rappelées.

Les autres parties importantes du processeur

La pré-extraction matérielle des données. C'est un système qui anticipe les besoins du processeur

en données en fonction des flux d'instructions exécutés. Elle transfère ces données à une mémoire cache

haut débit intégrée à la puce, où elles sont plus vite accessibles, afin d'accélérer l'exécution des

applications. ("Elle va chercher les données avant que le processeur n'en ait besoin.")

Les TLB. TLB signifie Translation Look-aside Buffers. Les buffers TLB de l'architecture

QuantiSpeed rapprochent les données critiques du processeur afin d'éviter que ce dernier n'ait à attendre

les données dont il aura besoin ultérieurement. Ces buffers évitent la duplication des informations et

libèrent plus d'espace sur le cache L2 pour laisser de la place à d'autres données attendues elles aussi par

le processeur. Ils permettent de calculer plus d'instructions par cycle.

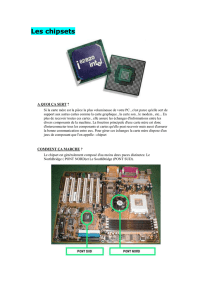

Le BARTON, "dernier" de l'architecture K7

"Dernier", n'est pas à prendre a la lettre, car il y a l'arrivée du Sempron, qui est apparu pour

marquer la fin du socket A. Cependant, ce proc n'est rien d'autre qu'un TBred qui s'adapte sur les sockets

A, 754 et 939 (sans pour autant supporter la technologie 64 bits)

Le core BARTON est le dernier issu de l'architecture Athlon XP K7 (32 bits). C'est le seul à

posséder 512 Ko actif de cache L2. Le Torthon en avait aussi 512, mais 256 Ko étaient bloqué. Il existe

cependant un moyen de les débloquer, mais ce n'est pas l'objet de ce topique.

Lorsque l'on compare un Athlon XP Toroughbred (256 Ko de cache) a un Barton (512 Ko) de

même Pro-Rating, on s’aperçoit que ce dernier possède une fréquence moins élevée. C'est tout

simplement dû au 256 Ko de cache supplémentaire. En effet, son cache lui permet de stocker plus

d'information et à donc moins souvent besoins d'accéder à la RAM du système, qui est beaucoup moins

rapide. Ce qui permet au processeur de calculer plus d'instructions par cycle, d'ou une baisse de fréquence

pour en arriver au même P-Rating. On peut voir la différence de la taille du core entre un T-Bred (256

Ko) et un Barton (512 Ko) sur la photo ci dessous.

Connaître les caractéristiques de son processeur

Pour connaitre absolument toutes les caractéristiques de votre processeur (très utile pour connaitre

d'avance si vous pouvez espérer overclocker votre proc), il faut regarder le n° de série qui se situe sur le

PCB de celui ci.

Vous relevez la première ligne a gauche, et on va voir a quoi ca correspond....

Pour commencer, on va prendre l'exemple du Toroughbred 2600+ FSB 133

AXDA DKV3C

A signifie qu'il s'agit d'un AMD Athlon (A = Athlon)

XDA signifie qu'il est gravé en 0,13µ. (XDA = 0,13µ XD = 0,18µ)

D veut dire que le package est en matière organique. (A = Matière céramique, D = Matière

organique)

K, c'est la valeur du vcore d'origine. (L =1.50V, U =1.55V, K =1,65V, M =1.75V)

V, c'est pour la température limite avant de cramer (V =85°C, T =90°)

3 indique la taille du cache L2 (1 =64Ko, 2 =128Ko, 3 =256Ko, 4 =512Ko)

C indique la valeur du FSB d'origine (C =133 MHz, D =166 MHz, E =200 MHz)

Certains softs permettent de connaitre ces N° une fois votre pc monté Central Brain Identifier et

OPN-462 vous donne toutes ces caractéristiques lorsque vous rentrez tout votre N° de série

Situer son processeur par rapport aux autres

Pour connaitre la capacité d'overclocking de votre processeur, il est très utile de le situer par rapport aux autres

proc de la même série. Il est important de savoir qu'AMD ne sort pas des 2200+ une semaine puis des 2400 la semaine

suivante, et aussi que les procs ne sont pas fabriqués sur des "chaines" différentes.

Les Processeurs sont tous fabriqués en même temps, et lors de la conception, rien ne les distingue,

puisqu’à ce stade, on ne sait même pas si un proc sera en 2500 ou 3200.... (Pour les Bartons)

Les processeurs subissent tout simplement des tests en fonction des demandes des clients. Par

exemple, s’il y a une commande de Bartons 3200+, AMD va tester plusieurs processeurs pris au hasard,

et leur faire subir des tests spécifiques au 3200+. Ceux qui passent sont programmés en 3200+ et vendus,

mais pour ceux qui ne l'ont pas passé, je ne sais pas si ils sont remis dans le stock pour d'autres tests

moins poussés (2500+ par exemple), ou si ils sont tous simplement bon pour la poubelle. Une chose est

sûre, un proc qui ne passe pas le test 2500+ ne resservira pas...

Le truc bien sympathique pour nous, les overclocker, c'est que si un processeur est testé en 2500+

(raison de forte demande par exemple), et bien il est vendu en 2500+, alors qu'il aurait peut être pu passer

le test des 3200+. C'est comme ca que l'on retrouve la plupart des 2500+ overclocké en 3200+ sans

augmentation de voltage. Bien entendu, il y a toujours de "mauvaises" séries qui montent seulement au

niveau des 2600 ou autres.... .Comme quoi, quand on dit que l'overclocking est aussi dû à la chance, c'est

bien vrai.

Tout ca pour faire comprendre que plus votre processeur n’est "petit" dans sa famille, est plus il à

de potentiel d'overclocking (sauf exceptions). Je dis bien potentiel, ca ne veux pas dire qu'il montera plus

haut qu'un haut de gamme de la série. Prenez l'exemple du 1800+, un des premiers T-Bred qui monte sans

soucis a plus de 1,4GHz @ 2 GHz la plupart du temps, mais aussi le 2600+ qui a la base est en 2,13 GHz,

et qui atteint souvent 2.4 ou 2.5 GHz (sauf exception). La montée en % est plus forte pour le bas de

gamme, mais celui ci reste majoritairement à une fréquence inférieure.

Donc pour situer votre proc, voila un tableau récapitulatif des différents processeurs gravés en

0,13µ et 0,18µ. Les 0,18µ étant moins intéressant pour l'overclocking. Bah oui, plus la gravure est grosse

et plus ca chauffe. (Cliquez pour agrandir)

Comment overclocker son PC à base d'un AMD Athlon XP

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

1

/

14

100%