Architecture des ordinateurs

1

Philippe Darche

IUT Paris Descartes

Année 2009-2010

Architecture des ordinateurs

14 - L’unité centrale

Philippe Darche 2 IUT Paris Descartes

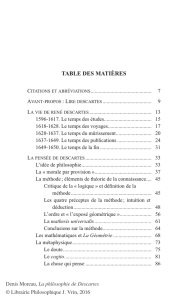

Le modèle de machine de Von Neumann

Appelée de manière raccourcie

« architecture Von Neumann »

D’après un rapport célèbre [Von Neumann 45]

(disponible sur le serveur de l’IUT)

Une abstraction (i.e. un modèle théorique)

Pour juste donner les détails nécessaires à la programmation

A ne pas confondre avec le modèle de calcul

Philippe Darche 3 IUT Paris Descartes

Modélisation de la machine de Von Neumann

E/S non représentées

Philippe Darche 4 IUT Paris Descartes

Modélisation de la machine de Von Neumann

Cinq éléments dans le rapport de [von Neumann 45]

Central Arithmetic Unité Arithmétique et Logique (UAL)

Central Control Unité de Contrôle (UCo)

Memory les différentes formes de mémoire

mémoire centrale

registres

Input interface et périphérique d’entrée

Output interface et périphérique de sortie

2

Philippe Darche 5 IUT Paris Descartes

Caractéristiques de ce modèle

Instructions et données dans la même mémoire

par opposition à l’architecture Harvard

Exécution séquentielle des instructions

Philippe Darche 6 IUT Paris Descartes

Un microprocesseur actuel

Xeon 7400 (6 cœurs)

Philippe Darche 7 IUT Paris Descartes

Une unité centrale du début

CPU (Central Processing Unit)

Un exemple : L’EDVAC

Appellation à ne pas confondre

avec le sens actuel

(i.e. le micro-ordinateur)

Philippe Darche 8 IUT Paris Descartes

Définition du MPU

Le microprocesseur = version intégrée

de l’unité centrale des années 50-70

MPU = MicroProcessor Unit

intégration de :

UCo + UT

mémoire cache

contrôleur de mémoire vive dynamique ou DRAM (2009)

mémoire vive dynamique (prochainement)

il ne reste plus que les contrôleurs d’E/S à intégrer

c’est déjà fait avec le micro-contrôleur !

3

Philippe Darche 9 IUT Paris Descartes

Définition du MPU

Composant programmable

Classification par application

à usage général (General Purpose Processor ou GPP)

microprocesseur à usage général

micro-contrôleur (MCU pour MicroController Unit)

intégration du CPU + mémoire + contrôleurs d’E/S

Spécialisé (Application-Specific Processor pour ASP

ou SPP pour Special Purpose Processor)

traitement numérique du signal

DSP (Digital Signal Processor)

ASIP pour Application-Specific Instruction set Processor

Philippe Darche 10 IUT Paris Descartes

Modélisation d’un microprocesseur

Philippe Darche 11 IUT Paris Descartes

Définitions de base

Chemin de donnée (data path)

ensemble des composants traversés

par les données

UAL (Unité Arithmétique et Logique) et FPU (Floating-Point Unit)

bus de donnée (data bus)

Chemin d’instruction (instruction path)

ensemble des composants traversés

par les instructions

UCo

bus d’instruction (instruction bus)

Microarchitecture = détails internes

Philippe Darche 12 IUT Paris Descartes

Une micro-architecture simple

à bus de donnée unique

4

Philippe Darche 13 IUT Paris Descartes

L’Unité arithmétique et logique

UAL ou ALU (Arithmetic and Logic Unit)

Calcul de fonctions unaires et binaires

arithmétiques : + et – (originellement) puis * et ÷aujourd’hui

logiques

ET, OU, NON et XOR

comparaisons : >, ≥, <, ≤ et =

décalages et rotations gauche et droite arithmétiques et logiques

Schéma de base

ACC = ACC + opérande

Résultat avec positionnement éventuel des indicateurs

voir transparent « cycle d’exécution de bas »

Philippe Darche 14 IUT Paris Descartes

Calcul des drapeaux

Philippe Darche 15 IUT Paris Descartes

Les registres utilisés par l’UAL

Le registre d'état ou des indicateurs

ou des drapeaux (flags)

CCR (Code Condition Register)

une partie seulement

Divers registres

le ou les accumulateurs

etc.

Philippe Darche 16 IUT Paris Descartes

Etats des indicateurs du registre d’état (1/2)

Etat temporaire (code condition)

jusqu'à la prochaine instruction risquant de modifier

l'indicateur concerné

renseignement sur la validité du résultat :

résultat nul, négatif, dépassement de format ou de capacité, etc.

5

Philippe Darche 17 IUT Paris Descartes

Le registre d'état du 8086

OF (Overflow Flag) : indicateur de dépassement

SF (Sign Flag) : indicateur de signe

ZF (Zero Flag) : indicateur de zéro

AF (Half carry Flag) : indicateur de demi-retenue

PF (Parity Flag) : indicateur de parité

CF (Carry Flag) : indicateur de retenue

OF DF IF TF SF ZF AF PF CF

D15 D0

Philippe Darche 18 IUT Paris Descartes

L’Unité de Contrôle

UCo

Organise l'exécution des instructions au rythme

d’un signal d’horloge Clk

génération des signaux de synchronisation internes

ou externes (bus de contrôle) du CPU

Philippe Darche 19 IUT Paris Descartes

Les registres utilisés par l’UCo

Le Compteur Ordinal (CO)

PC (Program Counter) ou IP (Instruction Pointer)

Le Registre d'Instruction (RI)

Le registre d'état ou des indicateurs

une partie seulement

Les registres d'index (IX)

Le pointeur de pile (SP)

Philippe Darche 20 IUT Paris Descartes

Etats des indicateurs du registre d’état (2/2)

Etat permanent

contrôle de l’UC

modification du comportement de certaines instructions

manipulation des caractères

modification du comportement du processeur

mode pas à pas

masquage des interruptions

⇒Concerne l’UCo

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

1

/

13

100%