Informatique - Enseirb

extrait_catalogue

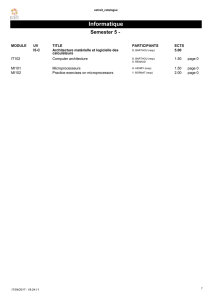

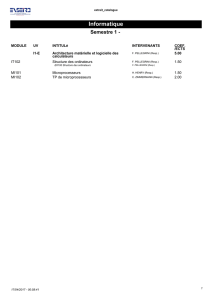

Informatique

Semester 5 -

MODULE UV TITLE PARTICIPANTS ECTS

I5-C Architecture matérielle et logicielle des

calculateurs D. BARTHOU (resp) 5.00

IT102 Computer architecture D. BARTHOU (resp)

S. RENAUD 1.50

MI101 Microprocesseurs H. HENRY (resp) 1.50

MI102 Practice exercises on microprocessors Y. BORNAT (resp) 2.00

17/04/2017 - 17:38:38 1

extrait_catalogue

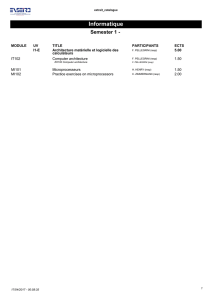

IT102 : Computer architecture

Shared by UV(s) :

I5-C Architecture matérielle et logicielle des calculateurs

ECTS credits :

1.50

Number of hours :

Lecture : 20.00

Individual work : 20.00

Teacher(s) :

BARTHOU Denis

RENAUD Sylvie

Title :

Computer architecture

Abstract :

This course is an introduction to computer architecture. It presents the essential hardware mechanisms in modern

architectures, exposing current limitations, evolutions of hardware architecture and its impact on software.

Plan :

This course is structured as follows:

- Micro arch and electronics evolution

- Representation of numbers, instructions. Implications on theory of information (Kleene rep. , undecidable

problems)

- Execution path

- Simple pipeline

- Improved pipeline (superscalar, VLIW, vector architectures)

- Memory (caches, prefetching, virtual memory)

- Examples of real machines

- I/O and various peripherals (disk, screen, printer)

- Multicore architectures

Prerequisite :

No prerequisite.

Evaluation :

A first training exam, with correction provided, and then a final exam.

Document(s) :

Lecture notes are given at the beginning of the course.

Keyword(s) :

Computer architecture, pipeline, cache memory, Moore's law

17/04/2017 - 17:38:38 2

extrait_catalogue

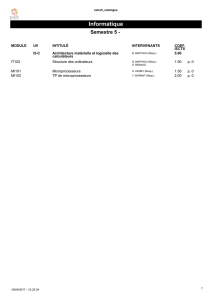

MI101 : Microprocesseurs

Shared by UV(s) :

I5-C Architecture matérielle et logicielle des calculateurs

ECTS credits :

1.50

Number of hours :

Combined lecture and tutorial classes : 28.00

Individual work : 15.25

Practical work : 21.00

Teacher(s) :

HENRY Hervé

Title :

Microprocesseurs

Abstract :

L'objectif du cours est de donner les éléments nécessaires à la

connaissance des microprocesseurs et à la pratique de la

programmation en langage machine.

Plan :

1. Système minimum

- logique trois-états, liaisons bidirectionnelles, bus et logique

de décodage, mémoires vives et mémoires mortes

- architecture interne du microprocesseur, instructions, données,

adresses cycles de lecture/écriture synchrone

2. Présentation du 68000

- composant et signaux

- structure interne, registres.

- jeu d'instruction, modes d'adressage et codage des instructions

- cycles de lecture et d'écriture asynchrones

3. Assembleur 68000

- instructions, champs et directives, étiquettes et opérandes

symboliques

- édition de liens

- instructions arithmétiques, indicateurs signés et non signés

- comparaisons et tests

- sous-programmes, piles, passage de paramètres, instruction LINK

4. Les exceptions

- exceptions logicielles, matérielles

- mécanismes communs

- étude détaillée des interruptions, mécanisme d'interfaçage aux

périphériques synchrones, asynchrones

5. Etude du circuit PIT 68230

- Différentes fonctions

- Périphérique parallèle, timer

- Demandes d'interruptions vectorisées.

17/04/2017 - 17:38:38 3

extrait_catalogue

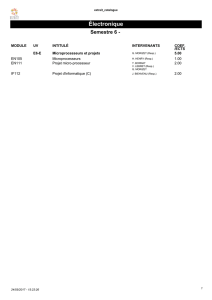

MI102 : Practice exercises on microprocessors

Shared by UV(s) :

I5-C Architecture matérielle et logicielle des calculateurs

ECTS credits :

2.00

Number of hours :

Individual work : 5.25

Practical work : 21.00

Teacher(s) :

BORNAT Yannick

Title :

Practice exercises on microprocessors

Abstract :

Practice exercises on ARM Thumb microprocessors using AT91 microcontroler series. These works are focused

on low level programming, physical layers communication and bases of operating system.

Prerequisite :

Cours de microprocesseur, algorithmique, programmation en C.

Evaluation :

Control during sessions

Document(s) :

Topics of practical exercises, programmers manual, components data sheets.

17/04/2017 - 17:38:38 5

1

/

5

100%