Sujets de Travaux Dirigés et de Travaux Pratiques - Lab

Université de Bretagne Occidentale - UFR Sciences - Département d’Informatique

Licence 1ère année (S1), Parcours 1

Introduction à l’Informatique

Sujets de Travaux Dirigés et de Travaux Pratiques

Pascal Ballet, Philippe Le Parc et Sophie Gire

TD 1 – Codage et Circuits logiques page 2

TD 2 – Architecture page 5

TD 3 et 4 – Variables, séquences et conditionnelles simples page 14

TD 5, 6 et 7 – Itérations (boucle Pour et Tant que) et tableaux page 17

TD 8 – Tableaux et graphisme page 20

TD 9 – Introduction aux bases de données page 22

TP1 – Introductions aux TPs et circuits logiques page 24

TP2 – Architecture page 31

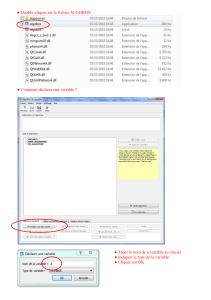

TP3 et 4 – Introduction à Visual Basic : variables, séquences et conditionnelles simples page 33

TP5 et 6 – Itérations (boucle Pour et Tant que) et tableaux page 45

TP 7 et 8 – Un peu de graphisme page 47

TP 9 – Introduction aux bases de données page 52

TP 10 – Gestion d’un stock de voitures page 55

Memo Access page 59

Retrouver ce document, et d’autres informations sur cet enseignement, dans l’Intranet du département

Informatique (intranet-depiup.univ-brest.fr), rubrique Pédagogie, puis Licence 1, puis Introduction

à l’Informatique.

Les exercices de TD suivis par une étoile (*) sont considérés comme des exercices de base, dont la

compréhension est nécessaire.

1

Université de Bretagne Occidentale - UFR Sciences - Département d’Informatique

Licence 1ère année (S1), Parcours 1

Introduction à l’Informatique

TD n°1

Codage et Circuits Logiques

L'objectif de ce TD est, d'une part de mettre en pratique les notions de codage vues en cours (bases,

changement de base, implémentation) et d'autre part, des exercices sur les circuits logiques sont proposés

pour consolider les éléments vus en cours.

Partie 1. Codage

Exercice 1 *

a) Soit le nombre 110102, quelle est sa valeur en base 10 ?

b) Soit le nombre 3010, quelle est sa valeur en base 2 ?

Exercice 2

Enumérer les symboles utilisés pour les bases suivantes : 4, 8, 16

Exercice 3 *

Soient les nombres suivants : 10112, 10114, 10118.

a) Quels sont les nombres en base 10 correspondant ?

b) Quels sont leur écriture en base 2 ?

Exercice 4

Soient les nombres 32314, 5289, 40657

a) Donner leur écriture en base 10.

b) Donner leur écriture en base 2.

Exercice 5 *

Soient les nombres binaires suivants : 1110110100012, 10100111012, 1000010011110112.

a) Quels sont les nombres en base 8 correspondant ?

b) Quels sont les nombres en base 16 correspondant ?

2

Exercice 6 *

Soient les 2 octets suivants :

A : 1011 00012

B : 0001 01112

On suppose que ces deux octets codent respectivement deux nombres.

1. Additionnez, en binaire, A et B

2. Quelle est la valeur entière de cette somme en base 10 ?

3. Additionnez, en binaire, B avec lui-même ? Que remarquez-vous sur le résultat ?

Exercice 7 *

a) Soit N le nombre suivant en base 10 : -29,25

1. Convertir la partie entière de la valeur absolue de N en binaire.

2. Convertir la partie fractionnaire de N en binaire.

3. Ecrire N en binaire.

4. Ecrire N sous la forme exponentielle binaire normalisée.

5. Donner une représentation interne de N en utilisant la forme suivante :

1 bit de signe (mantisse) / 11 bits pour la mantisse / 1 bit de signe (exp) / 3 bits pour l'exposant.

b) Recommencer l'exercice avec les nombres : 128,125 puis 0,8.

Exercice 8

Additionner les nombres binaires suivants : 0011 0011 et 0101 1111. Donner la valeur en base 2 et en

base 10 du résultat obtenu.

Exercice 9

Soit la suite de bits : 0101 1001 0000 0100.

a) Si l’on considère que cette suite de bits est un nombre entier codé en base 2, donner sa valeur en

base 16.

b) Si l’on considère que cette suite de bits est un nombre réel, codé avec le format vu en cours et

rappelé ci-dessous, donner sa valeur en base 10.

Signe (1 bit)

Mantisse (11 bits)

Exposant (3 bits)

Signe (1 bit)

Signe (1 bit)

Mantisse (11 bits)

Exposant (3 bits)

Signe (1 bit)

3

Partie 2 - Circuits logiques

Exercice 1 *

Donner les tables de vérité des portes ET, OU, OU exclusif et NON

Exercice 2 *

Soit le circuit suivant :

a) Donner une expression logique de la sortie S en fonction des entrées A, B, C et D.

b) Donner la table de vérité de la sortie S.

c) Donner une expression logique de la sortie S directement à partir de la table de vérité.

d) Simplifier l'écriture de S (choisir l'expression (a) ou (c)).

e) Proposer un circuit plus petit mais équivalent à celui proposé (on pourra également diminuer le

nombre d'entrées si possible).

Exercice 3 *

Soit l'expression logique suivante : S = A.B.C + (~A).B + A.(B+C)

a) Donner un circuit logique équivalent à cette expression.

b) Simplifier l'expression de S et donner un nouveau circuit logique.

Exercice 4 *

Soit le circuit logique suivant :

a) Donner la table de vérité de ce circuit

b) Quelle fonction assure ce circuit ?

c) Modifier ce circuit logique pour qu'il assure complètement sa fonction.

Exercice 5

Soit l’expression logique suivante : S =A.~B + (Ã.B + C)

Dessiner un circuit logique équivalent et donner la table de vérité. Après analyse la table de vérité,

donner une expression plus simple équivalent à S.

Exercice 6

Soit le circuit logique suivant :

a) Donner la table de vérité de ce circuit.

b) Donner une expression logique équivalente à ce circuit.

A

B

C

D

S1

S2

S

B

A

C

S

4

Université de Bretagne Occidentale - UFR Sciences - Département d’Informatique

Licence 1ère année (S1), Parcours 1

Introduction à l’Informatique

TD n°2

Architecture

L’objectif de ce TD est l’étude d’une architecture à jeu d’instructions réduit (RISC) simplifiée.

L’architecture est décrite en fin d’énoncé de TD

Exercice 1 *

A l’aide de la description de l’architecture RISC que vous trouverez en fin de sujet, donner, pour chaque

notation de constante uimm4, uimm5, simm5, uimm11, l’intervalle de valeurs que peuvent prendre ses

constantes.

Exercice 2 *

On considère les deux instructions en assembleur :

• addi rd, rs, simm5 qui additionne une constante sur 5 bits (simm5) à un registre source (rs)

et place le résultat dans un registre destination (rd). Nous supposerons que les registres sont sur

16 bits.

• add rd, rs1, rs2 qui additionne les valeurs des registres sources (rs1) et (rs2) et place le

résultat dans un registre destination (rd). Nous supposerons que les registres sont sur 16 bits.

a) Sachant que les registres sont sur 16 bits, decrire ce que l’ordinateur doit faire au moment de

l’éxécution de : addi rd, rs, simm5.

b) On suppose initialement que le registre r1 est à : 0000000000100011 et que le registre r3 est a :

0000010000111100. On exécute alors les deux instructions ci-dessous l’une après l’autre.

addi r2, r1, 15 (étape 1)

add r2, r3, r2 (étape 2)

Une fois l’étape 1 effectuée, quel est le contenu de r2 (écrit sur 16 bits) ? Quelle est la valeur de

r2 en base 10 ?

c) Une fois les étapes 1 et 2 effectuées, quel est le contenu de r2 (écrit sur 16 bits) ?

Exercice 3 *

On suppose les instructions suivantes chargées en mémoire (à partir de l’adresse mémoire 0) :

0) addi r1, r0, 0

1) addi r2, r0, 0

2) st (r2 + 15), r1

3) addi r2, r2, 1

4) add r1, r1, r2

5) addi. r3, r2, -6

6) bne -5

7) st (r2 + 15), r1

Décrire l’exécution de ce programme, en détaillant chaque étape de chaque instruction et en donnant les

valeurs de chaque registre.

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

1

/

64

100%