division

TD/TP circuits et architectures logiques

2014

1

1A Circuits logiques

DIVISION

Objectifs :

Concevoir, simuler et synthétiser un circuit logique pour la division de deux nombres de 4 bits.

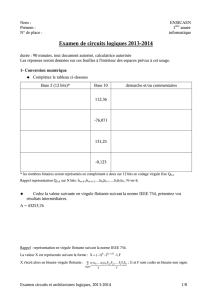

1. Présentation du sujet

1.1 Rappel opération de division

opérateur arithmétique structuré cascadable ou

complexe reposant sur les autres opérateurs.

Toutefois, comme pour les autres opérateurs, le

la division

ière de diviser 2 nombres à la

main. Un exemple est illustré en Figure 1. En

base 10, le diviseur multiplié par des puissances de 10 est soustrait au dividende autant de fois que

possible.

En base 2, les multiplications sont avantageusement remplacées par des décalages à gauche.

implémentation de la division reprend cette démarche. Elle peut être réalisée de façon logicielle

(soft) sur une UAL donnée ou matérielle (hard). Une réalisation hard

optimisée et donc plus rapide. Ce TD/TP a pour objectif ce type de réalisation hard de diviseur.

1.2 Algorithme de division

Non Restoring Division Algorithm).

Les étapes de cet algorithme sont décrites ci-dessous et un exemple suit dans le tableau 1.

Algorithme de division sans restauration :

Décalage des registres P et A de 1 bit vers la gauche.

Si le contenu du registre P est négatif :

on additionne le contenu du registre B à P

Si le contenu du registre P est positif :

on soustrait le contenu du registre B à P

Si le résultat chargé dans P est négatif on met le bit de poids faible de A (A0) à « 0 » sinon à « 1 ».

Ces étapes sont répétées N fois, N étant le format des données, ici N=4.

Figure 1 : exemple de division en base 10.

156=12*10+3*12.

TD/TP circuits et architectures logiques

2014

2

Opération élémentaire

P

P4P3P3P1P0

A

A3A2A1A0

Commentaires

Chargement des

registres

00000

0111

Initialisation des registres. Chargement du

dividende (A) et du diviseur (B)

décalage

00000

111-

décalage P,A de 1 bit à gauche

-B

11110

111-

-B)).

A0<=0

11110

111

0

résultat <0, A0 mis à « 0 ».

décalage

11101

110-

décalage P,A de 1 bit à gauche

+B

00010

110-

P<0, on additionne le diviseur B (P+B).

A0<=0

11111

1100

résultat <0, A0 mis à « 0 ».

décalage

11111

100-

décalage P,A de 1 bit à gauche

+B

00010

100-

P<0, on additionne le diviseur B (P+B).

A0<=1

00001

1001

résultat >0, A0 mis à « 1 ».

décalage

00011

001-

décalage P,A de 1 bit à gauche

-B

11110

001-

-B)).

A0<=1

00001

0011

résultat >0, A0 mis à « 1 ».

quotient

Tableau 1: Algorithme de division sans restauration. Exemple de la division de 7 (0111) dans le registre A par 2 (0010)

dans le registre B. Remarque -2 (11110). Le

quotient obtenu 0011 (3) corresponde au résultat de la division de 7 par 2.

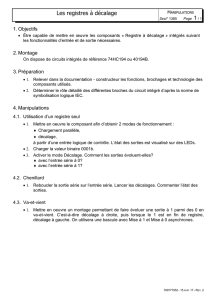

2. Implémentation matérielle

2.1 Présentation de la structure générale de l’implémentation matérielle

matérielle ogique avec une unité

de traitement (UT) dédiée aux opérations élémentaires et une unité de contrôle (UC) chargée de la

piloter. Une structure de ce type, celle utilisée dans ce TD/TP, est illustrée en Figure 2. La demande de

division, DIVstart, provient d

locale de la division hardware

CPU qui vient chercher les résultats de la division quand le signal DIVend est actif.

Figure 2: Schéma bloc de l’implémentation matérielle de la division.

TD/TP circuits et architectures logiques

2014

3

nt choisie est décrite dans la Figure 3. Elle comprend 3 registres de données et un

additionneur/soustracteur. Les registres possèdent tous une commande de chargement (LOADA,

LOADB, LOADP). Le registre A de 4 bits utilisé pour charger initialement le dividende possède

également une commande de décalage (SHIFTA) et une commande pour le chargement du bit de poids

faible A0 (LOADA0). Le registre P de 5 bits, pour le stockage des résultats intermédiaires, possède

aussi une commande de décalage (SHIFTP). Par ailleurs, une commande RESETP permet

lialisation à « 00000 » de ce registre.

Figure 3: Architecture de l'unité de traitement implémentant l'algorithme de division A/B pour la division du contenu du

registre A (dividende) par le contenu du registre B (diviseur). Le résultat de la division (quotient) se trouve dans le registre A

à la fin de l’opération. P est un registre de travail initialisé à zéro et stockant les résultats intermédiaires d’addition de

soustraction et de décalage.

2.2 L’unité de contrôle

2.2.1 Questions préalables

Les commandes

̅

̅

̅

̅

̅

̅

̅

et la valeur du bit A0 sont déterminées par les signes du contenu du

-soustracteur. Les sorties signe sont à « 1 » pour un nombre

négatif et à « 0 » pour un nombre positif ou nul (représentation en complément à deux).

Q.1 Exprimez

̅

̅

̅

̅

̅

̅

̅

et la valeur de A0 à charger en fonction des bits de signe de P et du

résultat

Q.2 Comment sont obtenues les sorties signe de P et ?

TD/TP circuits et architectures logiques

2014

4

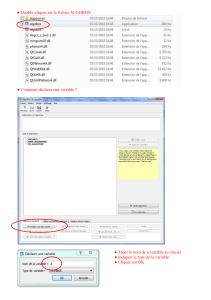

2.2.2 Conception de l’unité de contrôle

Concevez la machine La conception devra

appuyer sur le tableau t

Le signal DI valeur du quotient à la fin de

Une sortie DIVend indique quand le résultat est disponible.

Les commandes LOAD effectuent le chargement des valeurs présentes en entrée des registres (B, P, A

et A0

commande RESETP met à 00000 le contenu du registre P.

La période de cadencement, clk, de la machine supérieure au temps de

Figure 4: Schéma bloc de la machine à états finis contrôlant l'algorithme de division

description

état/cycle

LOADB

RESETP

SHIFTP

LOADP

SHIFTA

LOADA

LOADA0

DIVend

division terminée, attente DIVstart

0

0

0

0

0

0

0

0

1

début division, chargement registres

1

1

1

0

0

0

1

0

0

Après analyse, des simplifications sont possibles et finalement, seuls 4 signaux de sortie pour lunité

de contrôle sont nécessaires (voir la figure 5) pour piloter lunité de traitement dont le schéma est

présenté en figure 5.

Exprimez LOADcalc, LOADinit et SHIFTAP en fonction de LOADB, RESETP, SHIFTP, LOADP, SHIFTA,

LOADA, LOADA0.

TD/TP circuits et architectures logiques

2014

5

Figure 5: Schéma bloc de la machine à états finis simplifiée contrôlant l'algorithme de division

Figure 6: Schéma de l’unité de traitement fournie.

2.2.3 Synthèse de l’unité de contrôle

Synthétisez

1

/

5

100%