Architecture des ordinateurs : Câblage des processeurs dans l

1© 2014,2016 F. Pellegrini

Architecture des ordinateurs :

Câblage des processeurs

dans l'environnement « y86 »

(INF155)

F. Pellegrini

Université de Bordeaux

Ce document est copiable et distribuable librement et gratuitement à la condition expresse que son contenu ne soit modifié en

aucune façon, et en particulier que le nom de son auteur et de son institution d'origine continuent à y figurer, de même que le

présent texte.

2© 2014,2016 F. Pellegrini

Modélisation du câblage du y86

Modélisation du câblage du y86

L'environnement pédagogique y86 couvre aussi

L'environnement pédagogique y86 couvre aussi

le câblage du processeur y86 lui-même

le câblage du processeur y86 lui-même

Câblage modélisé par un langage dédié : HCL

Câblage modélisé par un langage dédié : HCL

(«

(« Hardware Control Language

Hardware Control Language »)

»)

Simplification de langages tels que Verilog et VHDL

Simplification de langages tels que Verilog et VHDL

Compilation du HCL en C et intégration du code

Compilation du HCL en C et intégration du code

produit au sein de l'émulateur y86

produit au sein de l'émulateur y86

œPermet de mettre en uvre plusieurs câblages du

œPermet de mettre en uvre plusieurs câblages du

même jeu d'instructions

même jeu d'instructions http://csapp.cs.cmu.edu/

3© 2014,2016 F. Pellegrini

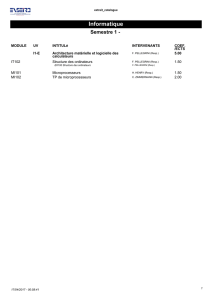

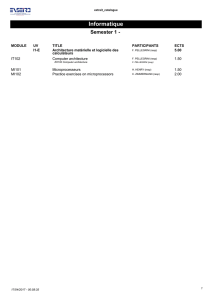

Utilisation de HCL

Utilisation de HCL

Description HCL

Description HCL

Compilateur HCL

Compilateur HCL

Description C

Description C

Liaison avec l'environnement

Liaison avec l'environnement

Simulateur y86

Simulateur y86

4© 2014,2016 F. Pellegrini

Syntaxe HCL (1)

Syntaxe HCL (1)

HCL permet de représenter le câblage des

HCL permet de représenter le câblage des

blocs fonctionnels du processeur y86

blocs fonctionnels du processeur y86

Syntaxe proche du langage C

Syntaxe proche du langage C

Types de données supportés :

Types de données supportés :

Booléens : type « bool »

Booléens : type « bool »

Signaux pilotant le fonctionnement des unités

Signaux pilotant le fonctionnement des unités

fonctionnelles du processeur

fonctionnelles du processeur

Valeurs entières (au plus 32 bits) : type « int »

Valeurs entières (au plus 32 bits) : type « int »

…Servent à coder les opérandes, adresses, …Servent à coder les opérandes, adresses,

5© 2014,2016 F. Pellegrini

Syntaxe HCL (2)

Syntaxe HCL (2)

Opérations supportées :

Opérations supportées :

Fonctions logiques sur des valeurs booléennes

Fonctions logiques sur des valeurs booléennes

Fonctions logiques sur des valeurs entières

Fonctions logiques sur des valeurs entières

Certains blocs fonctionnels ne font pas partie

Certains blocs fonctionnels ne font pas partie

du périmètre du langage :

du périmètre du langage :

Banque multi-ports des registres («

Banque multi-ports des registres (« register file

register file »)

»)

Mémoire centrale (instructions et données)

Mémoire centrale (instructions et données)

UAL

UAL

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

1

/

25

100%