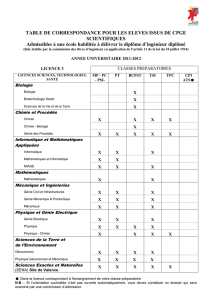

Comment organiser la mémoire physique

Noyau d'un système d'exploitation

INF2610

Chapitre 7 : Gestion de la mémoire

Noyau d'un système d'exploitation Génie informatique et génie logiciel

Ecole Polytechnique de Montréal Chapitre 7- 2

Chapitre 7 - Gestion de la mémoire

•Généralités

•Comment organiser la mémoire physique ?

•Comment organiser l’espace d’adressage d’un processus ?

•La pagination pure

Conversion d’adresses virtuelles en adresses physiques

Table des pages à plusieurs niveau et table inversée

Algorithmes de remplacement de page

•Segmentation / pagination

•Linux

Noyau d'un système d'exploitation Génie informatique et génie logiciel

Ecole Polytechnique de Montréal Chapitre 7- 3

Généralités

•Le gestionnaire de la mémoire est le composant du système d’exploitation

qui se charge de gérer l’allocation d’espace mémoire aux processus :

Comment organiser la mémoire physique ? (Partitions fixes ou variables,

cadres de même taille).

Comment mémoriser l’état de la mémoire? Parmi les parties libres en

mémoire, lesquelles allouer au processus? (politique de placement)

Faut-il allouer tout l’espace nécessaire avant l’exécution ou à la demande

? (politique d’allocation).

S’il n’y a pas assez d’espace en mémoire, doit-on libérer de l’espace en

retirant des parties ou des processus entiers ? Si oui lesquels ?

(politique de remplacement).

Les adresses figurant dans les instructions sont-elles relatives

(logiques /virtuelles) ? Si oui, comment les convertir en adresses

physiques.

Si plusieurs processus peuvent être résidents en mémoire, comment

assurer la protection des processus (éviter qu’un processus soit altéré

par un autre) ?

Noyau d'un système d'exploitation Génie informatique et génie logiciel

Ecole Polytechnique de Montréal Chapitre 7- 4

Généralités (2)

Exigences :

•Efficacité : la mémoire doit être allouée équitablement et à moindre coût tout en

assurant une meilleure utilisation des ressources (mémoire, processeurs et

périphériques).

•Protection : Les processus ne peuvent pas se corrompre.

•Transparence : Chacun des processus doit ignorer l’existence des autres en

mémoire.

•Relocalisation : la possibilité de déplacer un processus en mémoire.

Noyau d'un système d'exploitation Génie informatique et génie logiciel

Ecole Polytechnique de Montréal Chapitre 7- 5

(Algorithmes de gestion de mémoire)

Taille fixe (e.g. pages, blocs sur disque): on peut maintenir une liste

des objets libres ou une carte (bitmap).

Taille variable: on peut maintenir une liste des objets libres et chercher

(premier assez gros, taille la plus proche...); on peut avoir différentes

listes pour différentes catégories de tailles (algorithme des

subdivisions).

Ramasse-miettes (garbage collection): déterminer automatiquement la

mémoire libérée (décompte de référence, marquage et balayage,

compaction, copie, par générations).

Le noyau Linux utilise plusieurs de ces algorithmes (liste des objets

libres, subdivisions, décompte de référence) et maintient des réservoirs

de mémoire libre par processeur.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

1

/

63

100%