Conception d`un CAN 4 bits

Rapport de projet de design mixte

Jonathan AMIACH

Julien POITRAT

Rapport de projet de design Design d'un CAN 4 bits

Rapport de projet de design mixte

Conception d'un C.A.N.

4 bits

technologie AMS 0.35 µm

Rapport de projet de design mixte

Jonathan AMIACH

Julien POITRAT

Rapport de projet de design mixte Page 2 / 72

Rapport de projet de design mixte

Jonathan AMIACH

Julien POITRAT

Table des matières

1.Introduction....................................................................................................................................... 8

2.Présentation du projet........................................................................................................................ 9

1.Schéma bloc total .......................................................................................................................10

2.Cahier des charges du projet.......................................................................................................11

3.Étude de la partie analogique.......................................................................................................... 12

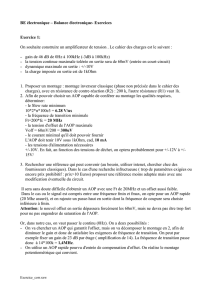

1.Étude du générateur de rampe analogique..................................................................................12

1.Choix du gain de l'AOP ........................................................................................................ 12

2.Détermination du slew rate de l'AOP ....................................................................................13

3.Détermination du produit gain/bande passante de l'AOP ..................................................... 13

4.Dynamique d'entrée de l'AOP ...............................................................................................13

5.Dynamique de sortie de l'AOP ..............................................................................................14

6.Étude en fréquence de l'AOP................................................................................................. 14

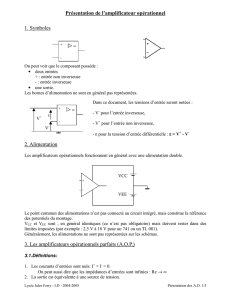

1.Paire différentielle............................................................................................................. 14

2.Détermination des pôles et des zéros................................................................................ 14

7.Spécifications et dimensionnements de l'AOP.......................................................................15

1.Spécifications de l'AOP.....................................................................................................15

2.Dimensionnement au premier ordre de l'AOP.................................................................. 17

1)Placement des pôles..................................................................................................... 17

2)Choix de la longueur des MOSFETs............................................................................18

3)Choix de la capacité Cc ...............................................................................................18

4)Détermination de I5......................................................................................................18

5)Dimensionnement de M3 ............................................................................................ 19

6)Dimensionnement de M1 et M2 ..................................................................................19

7)Dimensionnement de M5 ............................................................................................ 19

8)Dimensionnement de Mp ............................................................................................ 19

9)Offset systématique ..................................................................................................... 20

10)Dimensionnement de la source de courant Iext..........................................................21

11)Vérification de la dynamique de sortie.......................................................................21

12)Vérification du gain....................................................................................................21

8.Spécifications et dimensionnement du générateur de courant variable................................. 21

1.Spécifications.................................................................................................................... 21

2.Dimensionnement au premier ordre..................................................................................22

9.Capture du schematic de l'AOP dimmensionné au premier ordre......................................... 23

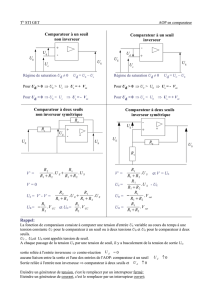

2.Etude du comparateur de tensions Vin et Vrampe..................................................................... 24

1.Choix de l'offset maximal du comparateur............................................................................ 24

2.Choix du slew rate du comparateur........................................................................................24

3.Choix du gain du comparateur............................................................................................... 24

4.Dynamique d'entrée du comparateur......................................................................................25

5.Dynamique de sortie du comparateur.................................................................................... 25

6.Spécifications et dimensionnement du comparateur..............................................................25

1.Spécifications du comparateur.......................................................................................... 25

2.Dimensionnement au premier ordre du comparateur........................................................ 25

Rapport de projet de design mixte Page 3 / 72

Rapport de projet de design mixte

Jonathan AMIACH

Julien POITRAT

1)Choix de la longueur des MOSFETs............................................................................25

2)Courant de sortie In...................................................................................................... 25

3)Dynamique de sortie.....................................................................................................26

4)Condition d'offset systématique................................................................................... 26

5)Gain de la paire différentielle.......................................................................................26

6)Dimensionnement de M3............................................................................................. 26

7)Dimensionnement de M1, M2......................................................................................27

8)Dimensionnement de M5............................................................................................. 27

9)Dimensionnement de M6............................................................................................. 27

7.Capture du schematic du comparateur dimensionné au premier ordre..................................28

3.Etude de la partie numérique...................................................................................................... 29

1.Spécifications de la partie numérique.................................................................................... 29

2.Déterminations des équations de la partie numérique............................................................29

1.Equations du compteur......................................................................................................29

2.Equations des signaux d'états et des signaux internes.......................................................30

1)Retenue.........................................................................................................................30

2)Signal de Test............................................................................................................... 31

3)Comparaison.................................................................................................................31

4)Fin de conversion......................................................................................................... 31

5)Défaut de conversion....................................................................................................31

3.Capture du schematic en standard cells................................................................................. 31

1.Schematic du compteur 4 bits........................................................................................... 31

2.Schematic de la partie numérique..................................................................................... 32

4.Simulations, validations et améliorations des blocs........................................................................34

1.Validation du générateur de rampe.............................................................................................34

1.Dynamique d'entrée de l'AOP ...............................................................................................34

1.Présentation du protocole de validation............................................................................ 34

2.Résultats de simulation du premier dimensionnement......................................................35

3.Modifications apportées.................................................................................................... 35

4.Résultats des modifications apportées...............................................................................35

2.Offset et dynamique de sortie de l'AOP.................................................................................36

1.Présentation du protocol de validation.............................................................................. 36

2.Résultats de simulation du dimensionnement validant le premier point de contrôle........37

3.Gain et bande passante de l'AOP........................................................................................... 38

1.Présentation du protocole de validation............................................................................ 38

2.Résultat de simulation du dimensionnement validant les deux premiers points de contrôle

..............................................................................................................................................40

3.Modifications apportées.................................................................................................... 40

4.Résultats des modifications apportées...............................................................................42

4.Slew Rate de l'AOP................................................................................................................44

1.Présentation du protocole de validation............................................................................ 44

2.Résultat de simulation du dimensionnement validant les trois premiers points de contrôle

..............................................................................................................................................45

3.Modifications apportées.................................................................................................... 46

4.Résultats des modifications apportées...............................................................................47

Rapport de projet de design mixte Page 4 / 72

Rapport de projet de design mixte

Jonathan AMIACH

Julien POITRAT

5.Test fonctionnel du générateur de rampe...............................................................................48

2.Validation des spécifications du comparateur............................................................................ 49

1.Dynamique d'entrée du comparateur......................................................................................49

1.Présentation du protocole de validation............................................................................ 49

2.Résultats de simulation du premier dimensionnement......................................................50

2.Gain en boucle ouverte du comparateur................................................................................ 50

1.Présentation du protocole de validation............................................................................ 50

2.Résultats de simulation du dimensionnement validant le premier point de contrôle........51

3.Dynamique de sortie et offset du comparateur...................................................................... 52

1.Présentation du protocole de validation............................................................................ 52

2.Résultats de simulation du dimensionnement validant les premiers points de contrôle... 52

4.Slew rate du comparateur.......................................................................................................53

1.Présentation du protocole de validation............................................................................ 53

2.Résultats de simulation du dimensionnement validant les premiers points de contrôle... 54

3.Modifications apportées.................................................................................................... 55

4.Résultats des modifications apportées...............................................................................56

3.Rappel des dimensionnements finaux.........................................................................................60

1.Dimensionnement final de l'AOP ......................................................................................... 60

2.Dimensionnement final du comparateur................................................................................ 61

4.Validation des spécifications de la partie numérique................................................................. 62

1.Compteur 4 bits .....................................................................................................................62

2.Mémorisation sur Save...........................................................................................................62

3.Simulation totale de la logique ..............................................................................................63

5.Topologies des blocs : layout.......................................................................................................... 64

1.Layout de l'AOP ....................................................................................................................64

2.Layout du générateur de courant variable..............................................................................65

3.Layout du comparateur.......................................................................................................... 66

4.Layout de la partie numérique............................................................................................... 67

5.Layout final............................................................................................................................ 67

6.Simulation mixte............................................................................................................................. 68

7.Conclusion.......................................................................................................................................72

Rapport de projet de design mixte Page 5 / 72

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

1

/

72

100%