TP4: interruptions

Département IF / Architecture Matérielle

MSP430 TP4 : Interruptions matérielles

Introduction

L’objectif de ce TP est d’étudier un rouage essentiel dans le fonctionnement des ordinateurs, le mécanisme

des interruptions matérielles. En particulier, on va s’intéresser aux notions suivantes : requête d’interruption

(IRQ), vecteur d’interruption, masquage d’interruption, routine de traitement d’interruption (ISR), sauvegarde

de contexte, acquittement d’interruption.

Tous ces concepts sont situés à la frontière entre le logiciel et le matériel, vous aurez donc à utiliser

certaines facultés du langage C propres à la programmation sur machine nue : directives interrupt, fonctions

intrinsèques, programmation avec «assembleur en ligne».

Le prétexte est de programmer un chronomètre numérique, similaire à celui d’une montre bracelet. Votre

chronomètre se servira de l’écran LCD pour communiquer avec l’utilisateur, vous aurez donc à réutiliser

le code que vous avez écrit pendant les séances précédentes. À la fin du TP, l’utilisateur pourra contrôler

le chronomètre (marche/arrêt, remise à zéro) grâce aux deux boutons de la carte mère. Pour la mesure

du temps proprement dite, on va faire appel à un nouveau type de périphérique, le timer. Ce TP est donc

également l’occasion d’illustrer la différence entre les notions de timer, de signal d’horloge, et de générateur

d’horloge.

Dans un premier temps, lisez l’encadré ci-dessous, pour vous rafraîchir la mémoire sur les différentes

notions mises en jeu.

À savoir : scrutation VS interruptions, requêtes (IRQ), vecteur, routine de traitement (ISR)

La communication entre un périphérique et le processeur se fait en général au travers des registres

matériels. Un composant qui veut transmettre une information au programme place cette information

dans un de ses registres, et attend que le processeur vienne lire cette valeur. C’est cette technique,

appelée scrutation (en anglais polling) que vous avez utilisée dans un TP précédent pour connaître

l’état des boutons. Un inconvénient majeur de cette approche est son incapacité à passer à l’échelle :

pour ne pas rater un évènement, le programme doit continuellement aller scruter l’état du matériel,

ce qui monopolise le processeur.

L’alternative consiste à mettre en place un mécanisme d’interruptions (cf poly page 73). Dans ce cas,

le composant qui veut transmettre une information au programme place cette information dans l’un

de ses registres, puis envoie au processeur une requête d’interruption (en anglais interrupt request

ou IRQ). Selon les architectures, ces requêtes peuvent transiter sur le bus principal ou sur des fils

dédiés appelés des lignes d’interruptions. Dans ce cas-là, soit le processeur dispose d’une entrée

pour chaque source d’interruptions, soit comme illustré ci-dessous, les lignes d’interruptions sont

concentrées par un périphérique dédié, appelé le contrôleur d’interruption.

CPU

Interrupt

controller Periph Periph

Periph PeriphPeriph

IRQ

system bus

1

Du côté du processeur, la gestion des interruptions est intégrée au cycle de Von Neumann. Lorsqu’il

reçoit une requête, le processeur interrompt automatiquement l’exécution du programme et saute

vers une adresse bien connue, à laquelle il s’attend à trouver une routine de traitement spécifique

(en anglais interrupt service routine ISR, ou interrupt handler ). Chaque ligne d’interruption est

ainsi associée à une routine distincte, ce qui permet au programmeur de prévoir un traitement

différent pour chaque type d’évènement. La correspondance {requête

n1→

routine

r1

, requête

n2

→

routine

r2

, etc.} est implémentée par une structure de données appelée la table des vecteurs

d’interruption (interrupt vector table ou IVT). En général il s’agit d’un tableau de pointeurs de fonction,

chaque case contenant l’adresse d’une ISR.

Une routine d’interruption est un morceau de code similaire à une fonction, sauf qu’elle est invoquée

automatiquement par le processeur, et non pas par un appel explicite. En plus de traiter l’évènement

proprement dit en allant lire et/ou écrire dans les registres du périphérique concerné, une ISR

devra typiquement accuser réception de l’interruption auprès du périphérique et/ou du contrôleur

d’interruption. Ensuite, elle peut se terminer et restaurer le contexte d’exécution, c’est à dire reprendre

l’exécution du programme interrompu, qui ne se sera aperçu de rien.

Exercice 1

Créez un répertoire TP4, et retapez dans un fichier tp4.c le programme suivant. Compilez-le

et transférez-le sur la carte.

#include "msp430fg4618.h"

#include "lcd.h"

unsigned int cpt;

int main(void)

{

lcd_init(); // Initialize screen

P5DIR |= 0x02 ; // Set P5.1 to output direction

cpt = 0;

for(;;)

{

volatile unsigned int i;

for(i=0;i<0xFFF0;i++) // software delay

{ // do nothing

}

lcd_display_number(cpt);

cpt++;

P5OUT = P5OUT ^ 0x02 ; // toggle P5.1 (LED4)

}

}

1 Prise en main du hardware timer

Pour mesurer l’écoulement du temps dans un ordinateur, deux solutions sont possibles :

— écrire une boucle logicielle, et espérer que processeur mette « un certain temps » à l’exécuter ;

—

utiliser un composant matériel capable de compter le temps, et qui nous préviendra quand la durée

voulue est écoulée.

La première solution, si elle convient parfaitement pour ajouter facilement des attentes grossières dans un

programme (et c’est ce qu’on a fait jusqu’ici) est difficile à rendre plus précise : il faut regarder finement

quelles instructions assembleur sont générées par le compilateur, chercher dans la documentation combien

de cycles d’horloge prend l’exécution de chaque instruction, maîtriser les conditions de sortie de boucle,

etc. Le travail de mise au point et de maintenance est considérable.

2

La seconde solution consiste à confier la temporisation proprement dite à un composant matériel, un

timer. En pratique, un timer est essentiellement constitué d’un compteur, c’est à dire un registre capable

d’incrémenter sa valeur sur commande. Si on dispose d’un signal oscillant à une fréquence bien connue

(c.à.d. un signal d’horloge) alors en branchant ce signal sur la «commande» du compteur, on obtient

effectivement une mesure du temps : le programme peut littéralement aller «lire l’heure» quand il en a

besoin. Mais, un timer est typiquement également capable de déclencher spontanément certaines actions

lorsque le temps imparti est écoulé (c’est à dire lorsque le compteur atteint une valeur prédéfinie), par

exemple d’envoyer une interruption au processeur.

Dans cette partie du TP, vous allez d’abord configurer le timer pour qu’il mesure la durée voulue, puis

l’interroger par scrutation (polling) depuis votre programme. Ensuite, dans la partie suivante, vous mettrez

en place un mécanisme d’interruptions. Commencez par lire les deux encadrés ci-dessous qui présentent

le fonctionnement du timer.

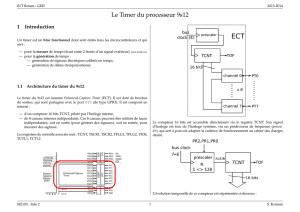

Extrait de la documentation : msp430x4xx.pdf pages 450 et 451

Timer_A is a 16-bit timer/counter with three or five capture/compare registers. Timer_A can support multiple

capture/compares, PWM outputs, and interval timing. Timer_A also has extensive interrupt capabilities.

Interrupts may be generated from the counter on overflow conditions and from each of the capture/compare

registers. Timer_A features include :

— Asynchronous 16-bit timer/counter with four operating modes

— Selectable and configurable clock source

— Three or five configurable capture/compare registers

— Configurable outputs with PWM capability

— Asynchronous input and output latching

— Interrupt vector register for fast decoding of all Timer_A interrupts

Timer_A Introduction

15-3Timer_A

Figure 15−1. Timer_A Block Diagram

CCR4

Compararator 4

CCI

15 0

CCISx

OUTMODx

Capture

Mode

CMx

Sync

SCS

COVlogic

Output

Unit4 DSet Q

EQU0

OUT

OUT4 Signal

Reset

GND

VCC

CCI4A

CCI4B

EQU4

Divider

1/2/4/8

Count

Mode

16−bit Timer

TAR

RC

Set TAIFG

15 0

TASSELx MCxIDx

00

01

10

11

Clear

Timer Clock

EQU0

Timer Clock

Timer Clock

TACCR4

SCCI Y A

EN

CCR1

POR

TACLR

CCR0

Timer Block

00

01

10

11

Set TA1CCR4

CCIFG

CAP

1

0

1

0

CCR2

CCR3

ACLK

SMCLK

TACLK

3

Utile pour le TP : vue simplifiée du Timer_A

Comme vous l’avez vu dans l’encadré page précédente, le timer possède un compteur principal

nommé TAR, et cinq blocs identiques dits de «comparaison et capture» nommés CCR0 à CCR4.

Chacun de ces blocs CCRx peut travailler soit en mode «capture», soit en mode «comparaison». Le

premier mode sert à chronométrer un évènement externe : la valeur de TAR est enregistrée dans

TACCRx à l’instant où se produit l’évènement. Le second mode sert à mesurer une durée : la valeur

de TAR est en permanence comparée à TACCRx, et le timer génère un évènement lorsque les deux

sont identiques (signal EQUx). Le timer est également capable de générer un signal PWM (noté

OUTx) mais nous ne nous y intéresserons pas.

Dans ce TP, on ne va utiliser que le canal CCR0, en mode Compare (bit CAP à zéro). Vous pouvez

donc ignorer la majorité du schéma page précédente pour ne retenir que cette version simplifiée :

Compararator

15 0

EQU0

Divider

1/2/4/8

Count

Mode

16−bit Timer

TAR

RC

Set TAIFG

15 0

TASSELx MCxIDx

00

01

10

11

Clear

Timer Clock

EQU0

TACCR0

TACLR

CCR0

Timer Block

Set TACCR0

CCIFG

CAP

1

0

ACLK

SMCLK

TACLK

Dans ce schéma, chaque petit carré noir est un booléen accessible depuis le logiciel via des

registres memory-mapped : il s’agit de respectivement de TACTL (Timer_A Control Register) et

de TACCTL0 (Capture/Compare Control Register). Bien sûr, les registres TAR et TACCR0 sont

également accessibles depuis le logiciel.

1.1 Choix de la base de temps

Comme expliqué dans l’encadré page suivante, notre timer compte des tops d’horloge, c’est à dire des

front montants d’un signal carré. Un multiplexeur nous permet de choisir entre plusieurs sources d’horloge :

TACLK est un signal externe, pris sur une patte d’entrées-sorties de la puce.

INCLK est le complément logique de TACLK.

ACLK est générée par le Clock Module de notre puce 1à une cadence de 32768Hz.

SMCLK est également générée par le Clock Module et va 32 fois plus vite que ACLK.

Exercice 2

On souhaite réaliser un chronomètre précis au centième de seconde. Pour chacune des

différentes sources d’horloge possibles, combien de cycles faudrait-t-il compter pour mesurer ces 10ms ?

Comme on va travailler uniquement en nombres entiers, il nous sera impossible de mesurer exactement la

durée voulue. Pour chaque possibilité, calculez la précision relative effectivement obtenue : de combien

notre chronomètre va-t-il se tromper à cause de l’erreur d’arrondi ? Exprimez vos différentes réponses en

ppm (partie par million) et aussi en secondes par jour.

1. Pour les plus curieux : allez voir la documentation du Clock Module, notamment le schéma page 290

4

Extrait de la documentation : msp430x4xx.pdf page 452

Timer_A Operation

15-4 Timer_A

15.2 Timer_A Operation

The Timer_A module is configured with user software. The setup and

operation of Timer_A is discussed in the following sections.

15.2.1 16-Bit Timer Counter

The 16-bit timer/counter register, TAR, increments or decrements (depending

on mode of operation) with each rising edge of the clock signal. TAR can be

read or written with software. Additionally, the timer can generate an interrupt

when it overflows.

TAR may be cleared by setting the TACLR bit. Setting TACLR also clears the

clock divider and count direction for up/down mode.

Note: Modifying Timer_A Registers

It is recommended to stop the timer before modifying its operation (with

exception of the interrupt enable, interrupt flag, and TACLR) to avoid errant

operating conditions.

When the timer clock is asynchronous to the CPU clock, any read from TAR

should occur while the timer is not operating or the results may be

unpredictable. Alternatively, the timer may be read multiple times while

operating, and a majority vote taken in software to determine the correct

reading. Any write to TAR takes effect immediately.

Clock Source Select and Divider

The timer clock can be sourced from ACLK, SMCLK, or externally via TACLK

or INCLK. The clock source is selected with the TASSELx bits. The selected

clock source may be passed directly to the timer or divided by 2, 4, or 8 using

the IDx bits. The clock divider is reset when TACLR is set.

1.2 Choix du mode de fonctionnement

Le Timer_A dispose de trois modes opératoires, décrits dans l’encadré page suivante : Up, Down, et

Continuous. Chaque mode spécifie une façon différente de compter jusqu’à l’échéance, et aussi quels

drapeaux (flags) seront levés lorsque le compteur atteint la bonne valeur. Les deux flags qui nous intéressent

sont nommés «TAIFG» et «TACCR0 CCIFG», et sont également memory-mapped, on va donc pouvoir aller

les consulter depuis le logiciel. Sous certaines conditions (dépendantes du mode de fonctionnement) le

timer lève l’un ou l’autre de ces flags pour indiquer qu’un évènement s’est produit.

Exercice 3

En vous aidant des extraits de documentation reproduits dans les pages suivantes, configurez

le timer pour qu’il lève un flag toutes les 10ms.

Exercice 4

Dans votre boucle principale, scrutez l’état du drapeau et n’incrémentez la variable

cpt

qu’à

chaque fois que le drapeau est levé. N’oubliez pas de le forcer ensuite à zéro.

Vous devez observer sur l’écran un compteur qui avance à la bonne vitesse. Faites valider par un enseignant.

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

1

/

22

100%