CPU - Parallélisme

Programmation Parallèle

sur CPU et GPU

(GPU=Graphics Processing Unit)

gael.guenn[email protected]

www.labri.fr/perso/guenneba/pghp_IO16

2

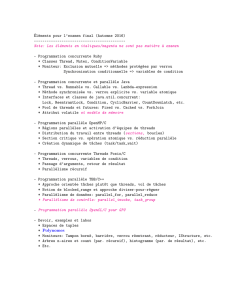

Plan du cours

•Motivations pour le parallélisme et les GPUs

–single core → multi-core → many-core

•CPU

–Architecture

–Modèle de programmation en mémoire partagé

•OpenMP

•GPU (Graphics Processing Unit)

–Architecture

–Modèle de programmation many-core

•CUDA

3

Objectifs

•Acquérir les bases pour

–éviter les erreurs de bases dans vos propres codes

•poursuivre en auto-formation au besoin

–échanger avec des spécialistes

–savoir comparer deux solutions matérielles

•savoir adapter le matériel aux besoins

4

Motivations applicatives

•Toujours plus de performance...

–plus rapide : de x10 à x100 ou plus !!

–résoudre des problèmes plus gros

–plus de précisions

–rendre possible de nouvelles applications, nouveaux algorithmes

–réduire la consommation

–etc.

5

Motivations applicatives

•Exemples :

–Simu électromag, en un point : intégration 4D

•Code initial en (mauvais) MatLab : 20min

•Code optimisé / CPU : 0.5s !!

–Simu sur GPU via MatLab : a life changer !

→ utilisation de CUDA en 3A-voie B (simu)

–3A-voie A (instrumentation) :

•Embarqué

–traitement/reconstruction efficace des données...

•Free-form optics

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

1

/

39

100%