cours ARM 1

09/03/2015 Jalil Boukhobza 1

Cours 8 Architectures &

Systèmes- introduction à l’ARM

Jalil Boukhobza

LC 206

boukhobza@univ-brest.fr

02 98 01 69 73

Plan du cours

1. Introduction

2. Versions et implémentations

3. Caractéristiques

4. Jeu d’instruction

5. Cycles d’exécution

6. Techniques de programmation

09/03/2015 Jalil Boukhobza 2

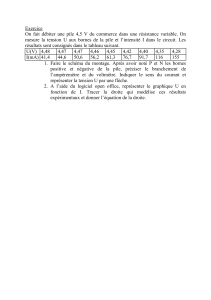

Ventes de l’ARM

09/03/2015 Jalil Boukhobza

http://chipdesignmag.com/sld/schirrmeister/2012/04/24/processor-architecture-enablement-betting-on-the-right-processor/

Introduction

ARM (Advanced Risc Machines): à l’origine Acorn Computer,

société anglaise

Concepteur d’ordinateur, 1er succès: ordinateur familial BBC

en 1982 (6502 proc 8 bits équipant le Apple II, 32KO de RAM

et cassettes…)

1983: début de travail sur la première version de l’ARM:

l’ARM1 (S. Furber, R. Wilson, et R. Heaton.

Objectif: proc 32bits RISC

Instruction de longueur fixe

Modèle Load/Store: opérations d’accès à la mémoire, sinon

instructions de calcul sur registres

Vu le jour en 1985 dans les VLSI Tech (25000 transistors).

09/03/2015 Jalil Boukhobza 4

Introduction, historique

ARM2:

Multiplication et multiplication/addition (traitement de

signal)

Interface co processeur pour le calcul flottant

Archimède, ARM2 à 8MHz

ARM: fondée en 1990: Apple, VLSI Technology,

Acorn Computer:

Définir un nouveau standard de processeur à faible

consommation et à faible coût

Premier développement: l’ARM6 (cœur version 3)

Adressage 32 bits, co processeur flottant, contrôleur vidéo.

09/03/2015 Jalil Boukhobza 5

Archimède, 1987

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

1

/

48

100%

![Mesure du rythme cardiaque IV] Signal lumineux modifié par le flux](http://s1.studylibfr.com/store/data/004744681_1-54c8bffa926fb8da8bcaec6bf73be081-300x300.png)