Nanoélectronique supraconductrice : la logique RSFQ

Nanoélectronique supraconductrice : la logique RSFQ

Alain GAUGUE et Alain KREISLER

Laboratoire de génie électrique des universités Paris 6 et Paris 11 (LGEP) UMR 8507 CNRS SUPÉLEC,

11 rue Joliot Curie, Plateau de Moulon, 91192 GIF/YVETTE Cedex

Résumé : L'électronique supraconductrice, fondée sur

un principe nouveau - la logique RSFQ (Rapid Single-

Flux Quantum) - connaît aujourd'hui un regain d'intérêt

du fait de ses performances exceptionnelles, très au delà

de celles des filières électroniques classiques. Cette

technologie, basée sur l'utilisation de jonctions

Josephson shuntées de dimensions submicrométriques,

offre comme principal avantage d'être ultra-rapide tout

en présentant une consommation ultra-réduite. De

nombreuses fonctions électroniques ont déjà été

réalisées et pourraient être amenées, au terme de la

prochaine décennie, à remplacer avantageusement les

circuits à base de semiconducteurs.

1 - Introduction

L’évolution de l’électronique fait une place de plus

en plus grande aux circuits logiques au détriment des

circuits analogiques. Cette croissance exponentielle de

l'électronique numérique en cette fin de siècle est sans

aucun doute due aux techniques de traitements

numériques de l'information omniprésentes dans notre

environnement quotidien (télécommunications,

multimédia, automobile, domotique, etc). Les besoins

sans cesse croissants en circuits numériques vont de plus

de pair avec des performances (densité d'intégration,

rapidité) de plus en plus élevées.

Les composants principaux des circuits logiques sont

aujourd’hui basés sur des technologies semiconductrices

sur silicium (transistors à effet de champ de type MOS).

Ces circuits intégrés ont suivi une progression

déterministe, régie par la loi de Moore, de sorte qu’il est

actuellement possible de réaliser des circuits intégrant,

sur une puce de silicium de l’ordre du centimètre carré,

plusieurs dizaines de millions de transistors fonctionnant

à plusieurs centaines de MHz et qu'il sera sûrement

possible, lors de la prochaine décennie, de réaliser des

processeurs avec des densités d'intégration de l'ordre de

2×109 Transistors/cm2 fonctionnant à une fréquence

d'horloge de 3 GHz. Néanmoins l’augmentation de la

densité d'intégration et de la rapidité des circuits se

heurtera inévitablement à la difficulté d’extraire la

puissance dissipée dans ces circuits et à des défis

technologiques (technologie 35 nm).

L'électronique supraconductrice [1,2], dès les années

60, a été présentée comme une alternative possible aux

semiconducteurs pour la réalisation de composants

logiques. En effet, cette technologie présente des atouts

indéniables pour la réalisation de composants ultra-

rapides : i) les lignes supraconductrices sont non-

dispersives ce qui permet de véhiculer des impulsions

électriques ultra-brèves (de l'ordre de la picoseconde)

sans aucune déformation ; ii) les temps de commutation

des jonctions supraconductrices (jonction Josephson)

sont de l'ordre de la picoseconde ; iii) la puissance

dissipée dans une cellule élémentaire est très faible.

Cependant, malgré des efforts considérables et des

projets de grande envergure - calculateur

supraconducteur de IBM (1969 - 83) et le projet MITI

au Japon (1981 - 90) - jusqu’à une date récente aucune

réalisation pratique n’a pu concurrencer les filières

électroniques traditionnelles, et cela pour plusieurs

raisons. Tout d’abord, il a fallu longtemps pour imaginer

une logique à supraconducteur présentant des

performances intéressantes. Jusqu'à la fin des années 80

les fréquences de fonctionnement étaient limitées aux

alentours du GHz, fréquences d’un ordre de grandeur à

Fré

q

uence d’horlo

g

e

1 THz

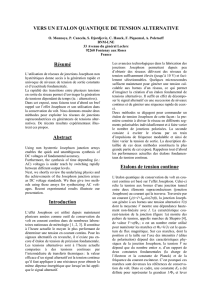

Figure 1 : comparaison, en terme de fréquence de

fonctionnement de système complexe (par exemple un

p

rocesseur), entre la filière semiconductrice et la filière

supraconductrice. Les données pour les semiconducteurs

sont issues de la National Technology Roadmap [3] et

celles pour les supraconducteurs du tableau I.

100 MHz

1 GHz

10 GHz

100 GHz

H

aut

T

c (65-77K) ???

supraconducteurs

B

as

T

c (4-5K) 30M JJ

0,4 µm

3M JJ

0,8 µm

300k JJ

1,5 µm 0

,

03

µm

10k JJ

3,5 µm 0,07 µm

semiconducteurs 0,13 µm

0,18 µm

0,20 µm

???

0,25 µm

- Litho. électronique

- UltraViolet Extrême

040

Lithographie optique

Années

1995 1998 2001 2004 2007 2010

peine plus élevée que celles des circuits

semiconducteurs. Ensuite, il a été difficile de développer

une technologie fiable pour réaliser les composants,

Enfin, durant ces deux dernières décennies, les

semiconducteurs ont vu leurs performances s’améliorer

sans cesse permettant toujours d’atteindre les objectifs

visés à un instant donné.

Néanmoins l'électronique supraconductrice, fondée

sur un principe nouveau - la logique RSFQ (Rapid

Single-Flux Quantum) [4] - connaît depuis peu un

regain d'intérêt du fait de ses performances

exceptionnelles, très au-delà de celles des filières

électroniques classiques (cf. figure1), qui par ailleurs se

rapprochent de leur vitesse limite. Ainsi, au terme de la

prochaine décennie, ces circuits pourraient être amenés

à remplacer avantageusement les circuits à base de

semiconducteurs tels que le prévoit l'autoritaire

prospective de la National Technology Roadmap for

Semiconductors [3].

2 - Composants logiques supraconducteurs

Avant l'apparition de la jonction Josephson, coeur de

tout composant logique supraconducteur actuel, les

dispositifs logiques (par exemple le cryotron) mettaient

à profit le changement de phase

supraconducteur/normal, permettant ainsi de commuter

entre un état faiblement résistif (normal) et un état

supraconducteur. De tels composants n'ont jamais

débouché sur des applications concrètes du fait des

principes thermiques intrinséque mis en jeu limitant par

là même les vitesses de commutation.

Au début des années 80, apparut une famille de

composants logiques, dénommée logique à maintien -

latching logic -, qui utilisait la commutation d'une

jonction Josephson présentant un effet d'hystérésis (cf.

figure 2). Cette hystérésis, nécessaire pour le maintien

des états logiques, nécessitait cependant la remise à zéro

périodique (et pendant un certain temps) du courant de

polarisation de la jonction, ce qui limitait

intrinsèquement la fréquence d'horloge des composants

aux alentours du GHz. Cette technologie ne perça donc

pas et le choix technique, qui consistait à imiter les

composants semiconducteurs, en codant les états

logiques par des tensions, fut remis en cause puis

abandonné.

La logique Rapid Single Flux Quantum fit alors son

apparition. Elle est fondée sur l'utilisation de jonctions

Josephson shuntées, donc non hystérétiques, et met à

profit, comme son nom l'indique, leurs comportements

dynamique et quantique (cf. figure 3). Dans les

composants RSFQ ce n'est pas un niveau statique de

tension qui code l'information, mais la présence ou

l'absence d'un quantum de flux magnétique (Fluxon)

F0 = h/2e = 2,07×10-15 Wb. La cellule élémentaire

RFSQ est constituée d'une boucle supraconductrice

fermée par une jonction et shuntée par une résistance.

Chaque variation d'un quantum de flux dans la boucle

(fluxon entrant ou sortant de la boucle) induit une

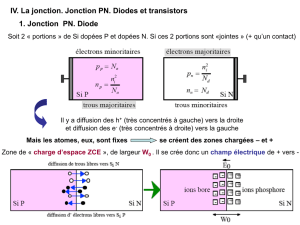

Figure 2 : principe de fonctionnement de la logique

à

maintien fondé sur l'utilisation d'une jonction Josephson

avec une caractérisitque I-V hystérétique. Le courant de

polarisation Ip de la jonction est fixé à une valeu

r

légèrement inférieure au courant critique Josephson Ij. L

a

j

onction commute de l'état supraconducteur (état 0), à un

état résistif (état 1), lorsqu’est appliqué un courant de

polarisation qui dépasse momentanément Ij. Pour revenir

à

l'état 0 il faut que le courant de polarisation soit ramené

à

zéro

p

endant un certain tem

p

s.

Courant état "1"

état "0"

IJ

Courant

état "0"

Ip

Jonction

Josephson

shuntée

Jonction

Josephson

Hystérésique

état "1"

I1 0Tension

0 V1 Tensio

n

Tension

Temps

État

"0"

État

"1"

État

"0"

Figure 3 : principe de fonctionnement de la logique RFSQ

fondé sur l'utilisation d'une jonction Josephson shuntée

avec une caractérisitque I-V non hystérétique. Lorsque le

courant de polarisation Ip atteint le courant critique

Josephson Ijde la jonction, un quantum de flux pénètre

dans la boucle ce qui induit une impulsion de tension aux

b

ornes de la jonction. Par convention, on définit l'état

logique 1 par la présence d'une impulsion durant l

a

p

ériode du signal d'horloge et, l'état 0 par l'absence d'une

impulsion durant la période du signal d'horloge.

Tension

État

"0"

Passage de

l’impulsion Temps

Horloge

État

"1"

État

"0" Temps

Données

impulsion de tension aux bornes de la jonction, dont la

valeur de l'intégrale temporelle est égale à F0 soit

2,07 mV×ps. La durée et l'amplitude de cette impulsion

dépendent de la géométrie de la jonction et du matériau

qui la compose; pour une jonction en Nb de 1 µm2

l'impulsion dure environ 1 ps et a 2 mV d'amplitude. Le

traitement des données revient donc à manipuler des

impulsions de tensions résultant du transfert de quantum

de flux, avec comme avantage que l'énergie dissipée lors

du transfert d'un quantum de flux est indépendante de

l'amplitude de l'impulsion et, est égale à Ij×F0 : soit pour

un courant critique Josephson de 100 µA, une énergie

de 2×10-19 J ; ce qui est 5 ordre de grandeur plus faible

que pour les semiconducteurs.

3 - Structure et performances

des composants RSFQ

Tout circuit RSFQ est constitué de trois cellules

élémentaires [2] (cf. figure 4). La première, composée

d'une inductance et d'une jonction, joue le rôle de buffer,

elle assure la transmission des impulsions picosecondes.

La seconde cellule, constituée également d'une

inductance et d'une jonction assure le stockage de

l'information (impulsion), sous forme d’un courant de

boucle persistant. Enfin, la troisième constituée d'une

inductance et de deux jonctions différentes, contrôlée

par un signal d'horloge, réalise deux fonctions. Tout

d'abord, elle joue le rôle de cellule tampon, qui empêche

un signal arrivant sur la sortie de réagir sur l'entrée et de

plus, assure la prise décision : transmettre ou non

l'information (impulsion). Les inductances associés aux

jonctions font partie intégrante de la fonction et servent

soit à coupler les différentes cellules entre elles (cf.

cellule 1), soit à stocker l’énergie (cf. cellule 2). Un

fonctionnement optimal est obtenu lorsque la relation

L×Ij = F0/2 est vérifiée (pour Ij ~ 100 µA, L ~ 10 pH).

Quant au signal d'horloge, il sert de référence aux

impulsions de tensions pour définir les états logiques 0

et 1. Par convention, l'état logique 1 est défini par la

présence d'une impulsion durant la période du signal

d'horloge et, l'état 0 par l'absence d'une impulsion durant

cette même période.

Les performances des composants RSFQ sont

intrinséquement supérieures à celles des composants

semiconducteurs, aussi bien sur les aspects rapidité et

énergie dissipée pour une même densité d'intégration.

La limite ultime de la fréquence de fonctionnement

d'un composant RSFQ réalisant une fonction logique

élémentaire (par exemple la bascule flip-flop) est fixée

par la largeur de l'impulsion créée par le fluxon, et peut

s'exprimer grâce à un modèle de type RSJ (Resistively-

Shunted Junction) [5] : FJ = wJ / 2p = (bc JJ /2pF0 CA)½,

où bc est le paramètre de McCumber fixé, en général,

par la résistance de shunt au voisinage de 1, Jj la densité

de courant critique Josephson et CA = C/A la capacité

spécifique du dispositif de surface A. L'épaisseur de la

barrière tunel est l’un des paramètres clefs (comme la

dimension de la jonction) des performances

fréquentielles des composants, car elle détermine la

densité de courant critique Josephson Jj. Sa diminution

augmente de manière linéaire avec CA et de manière

exponentielle avec Jj, ce qui fait que la fréquence de

fonctionnement fj croit comme ÖJj, d'où la nécessité

d'avoir des jonctions à fort Jj pour réaliser des

composant rapides. Pour des circuits asynchrones de

complexité moyenne, les fréquences de fonctionnement

sont comprises entre wJ/15 et wJ/10 (expression

empirique), mais peuvent être limitée entre wJ/60 et

wJ/25 pour des circuits très complexes (processeur, par

exemple) [5]. Les fourchettes de fréquences données

dans le tableau I et représenté figure 1 ne dépendent que

de la conception/implantation des composants RSFQ et

ne représentent nullement les limites physiques

théoriques.

La puissance consommée dans une porte logique

RSFQ est inférieure au µW. Elle est essentiellement due

au courant de polarisation de quelques centaines de µA

qui traverse les résistances environnentes (résistance de

polarisation, résistance de shunt). Dans les composants

actuels, la contribution due à l'énergie dissipée dans la

jonction Josephson reste négligeable (cf. ci-dessus, de

l'ordre de 2×10-19 J). Notons que la puissance ne peut

pas être minimisée en diminuant le courant de

polarisation, car le produit F0×IJ doit être toujours très

supérieur au produit kT sinon la contribution en terme

de bruit, dû aux fluctuations thermiques, n'est pas

négligeable ce qui entraîne un taux d'erreur bit

rédhibitoire pour la plus part des applications.

La densité d'intégration de jonction Josephson (en

Nb) réalisée à ce jours est de 60×103 JJ/cm2 [6], elle

n'est pas limité par les dimensions ultimes des jonctions,

mais surtout par la résistance de shunt qui vient

considérablement augmenter la surface de la cellule

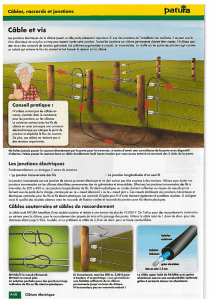

Transmission de

l'information

Inductance

Double jonctions

I

S

I

S

= Courant persistant

·

·

Prise de décision

Stockage de l'information

Sign al

d'horloge

Buffer

·

·

·

·

······

Polarisation

(continu)

Polarisation

(continu)

Polarisation

(continu)

Figure 4 : Structure de base d’une porte RFSQ constituée

de 3 cellules : buffer, stockage de l’information et prise de

décision.

élémentaire. En effet cette résistance nécessite une

surface comprise entre 50 et 200×D2, où D est la

dimension de la jonction [7]. Des travaux récents sur Nb

ont décrit la possibilité de réaliser des jonctions de

moins de 300 nm qui ne nécessite plus de résistance de

shunt (bc intrinséque ~ 1) [8]. De plus, l'utilisation de

processus planaire multicouches (8 couches de Nb au

lieu de 3 actuellement) permettrait de limiter la surface

d'une porte RSFQ à 25×D2, densité d'intégration

comparable à celle des composants semiconducteurs.

Avec une technologie à 0,3 µm, une densité théorique

de 40×106 JJ/cm2 pourrait êre atteinte, mais en pratique

ne pourrait pas dépasser 15×106 JJ/cm2 si on tient

compte des aspects thermiques.

4 - Conclusion

La technologie la plus mature actuellement est à base

de jonction tricouche en Nb. Ce matériau nécessite

cependant une température de fonctionnement de 4 à

5 K et est limité intrinsèquement à un temps de réponse

de 0,7 ps. Notons qu'à ce jour le circuit le plus rapide

(fréquence de l’ordre de 800 GHz) est une bascule Flip-

Flop réalisé en technologie niobium de 0,25 µm [9]. Par

ailleurs, le plus grand nombre de jonctions mis en

oeuvre, 90×103 JJ en technologie 1,75 µm, l'a été pour

la réalisation d'un microprocesseur devant fonctionner à

20 GHz [6]. Une alternative serait d'utiliser une

technologie NbN présentant l'avantage de fonctionner à

une température de l'ordre de 10 K et d'être

intrinsèquement 50 % plus rapide. Mais actuellement

elle ne permet pas de réaliser des applications avec plus

de 2×103 JJ. Enfin, la technologie YBaCuO, qui est loin

d'être maîtrisée, mais qui présente l'avantage de pouvoir

réaliser des jonctions non hystérétiques avec des temps

de réponse de 0,1 ps et de ne nécessiter qu'un

refroidissement vers 40-50 K. Cette température élevée

de fonctionnement engendre cependant un bruit

thermique excédentaire qui doit être obligatoirement

compensé par un courant de polarisation dix fois plus

élevé (car TYBCO = 10×TNb) qui a pour conséquence de

mettre en oeuvre des inductances dix fois plus petite, à

la limite des possibilités technologiques actuelle.

JJ D CA Fréquence de fonctionnement

en GHz pour un circuit :

µA/µm2 µm FF/µm2 unitaire standard complexe

10 3,54 50 124 52 – 78 13 – 31

20 2,50 54 169 71 – 106 18 – 42

40 1,77 58 230 97 – 145 24 – 58

100 1,12 64 346 145 – 217 36 – 87

200 0,79 70 468 196 – 294 49 – 118

500 0,50 80 693 290 – 435 73 – 174

1000 0,35 90 927 388 – 582 97 – 330

Tableau I : Caractéristiques et performances fréquentielles des

jonctions Josephson en fonction de leurs dimensions [5].

Type du

composant Nombre de

jonctions ×103 Applications

Processeur, DSP 100 – 300 Ordinateurs peta-

flops, SDR

Matrice de

commutation 10 – 300 Télécommunications

Corrélateur 10 – 300 Astronomie, radar

Convertisseur

A/D, D/A 1 – 10 Radar, SDR,

métrologie

Échantillonneur 0,1 – 1

Tableau II : Estimation des besoins en jonctions Josephson en

fonction des principaux composants numériques.

De nombreuses fonctions électroniques ont déjà été

réalisées : des boucles à verrouillage de phase, des

convertisseurs N/A et A/N, des mémoires, des

autocorrélateurs, des filtres, des processeur. Les besoins

en nombre de jonctions, pour une application donné sont

évalués dans le tableau II [10], mais de nombreux

progrès technologiques (et d'investissement financier!)

doivent encore être fait pour que l'électronique RSFQ

touche la production de masse.

Références

[1] K. Likharev, Superconductors speed up computation,

Physics World, 10 (5), 39-43 (1997)

[2] D. Brock, E. Track, J. Rowell, Superconductor Ics: the

100 GHz second generation, IEEE Spectrum, 40-46

(Dec 2000)

[3] voir http://public.itrs.net/

[4] K. Likharev, K. Semenov, RSFQ logic/memory family: a

new josephson-junction technology for sub-terahertz clock

frequency digital systems, IEEE Trans. Appl. Supercond 1(1),

3-28 (1991)

[5] A. Kleinsasser, High performance Nb Josephson devices

for Petaflops computing, IEEE Trans. Appl. Supercond 11(1),

1043-1049 (2001)

[6] M. Dorojevets, P. Bunyk, D. Zinoviev, FLUX chip:

Design of a 20 GHz 16 bit ultrapipelined RSFQ processor

prototype based on 1.75 µm LTS technology, IEEE Trans.

Appl. Supercond 11(1), 326-332 (2001)

[7] Y. Naveh, D. Averin, K. Likharev, Physics of high Jc

Nb/AlO/Nb Josephson junctions and prospects of their

applications, IEEE Trans. Appl. Supercond 11(1), 1056-1060

(2001)

[8] A. Kadim, C. Mancini, M. Feldman, D. Brock, Can RSFQ

logic circuits be scaled to deep submicron junctions?, IEEE

Trans. Appl. Supercond 11(1), 1050-1055 (2001)

[9] W. Chen, A. Rylyakov, V. Patel, J. Lukens, K. Likharev,

Rapid single flux quantum T-Flip Flop Operating up to 770

GHz, IEEE Trans. Appl. Supercond 9, 3212-3215 (1999)

[10] S. Tahara, S. Yorozu, Y. Kameda, Y. Hashimoto, H.

Numata, T. Satoh, W. Hattori, M. Hidaka, Superconducting

digital electronics, IEEE Trans. Appl. Supercond 11(1), 463-

468 (2001)

1

/

4

100%