Processeur JAP

Processeur JAP

3 rue de l’éperon - 77000 Melun

Tél : 01 64 52 16 96 - www.a-e-d.com

JAP Processor

Features

Bilingual processor : Java and C

2 instruction sets (Byte-Code, Native)

1 Java instruction/ Clock Cycle

1 Native instruction/ Clock Cycle

32 bits Architecture

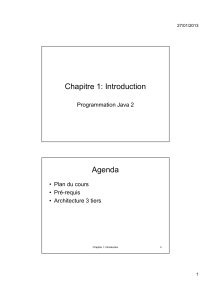

JAP

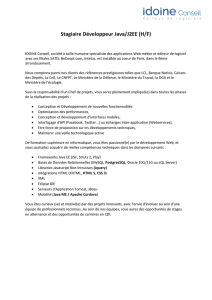

Processeur JAP 32 bits

Architecture

STACK CACHE

FSM

IR

PC

Interrupt

BP2

BP1

SP

(min,max)

Floating

Point

Unit

32/64

bits

IEEE

D31-0

AD23-0

Address data 24

Data 32

Address Prog 24

Interrupt 8

Program 32

P31-0 Intr0-7 AP23-0

AP

Caractéristiques

- Processeur 32 bits

- Architecture Pile

- Architecture Harvard

- Micro-machine

- 4 étages de pipeline

- FPU IEEE-754

- 1 micro-instruction / cycle

JAP

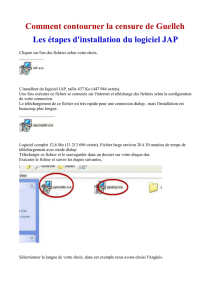

Outils

Simulateur

Compilateur C Assembleur

Système

d’exploitation

JOS

Environnement de

développement

JAVA

JAP

Avantages (hard)

Processeur bilingue (2 jeux d

(2 jeux d(2 jeux d

(2 jeux d’

’’

’instructions)

instructions)instructions)

instructions)

Instructions JAVA (« byte-code »)

Instructions natives (assembleur et C)

Ex

ExEx

Exé

éé

écution rapide

cution rapidecution rapide

cution rapide

Architecture Risc Harvard

Instructions Java et native exécutées en 1 cycle d’horloge.

Cache de donnée intégré directement dans l’architecture du processeur

S

SS

Sé

éé

écurit

curitcurit

curité

éé

é

2 modes : JAVA / Native (bit superviseur)

Pile JAVA sécurisée (pas besoin d’une MMU)

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

1

/

15

100%