rapport_projet riscvf

1

Projet M2 Pro CAMSI

Etude et réalisation d’un microprocesseur RISC 32 bits

Rodrigue Ndashimye, Ibrahima Djité

25/02/2013

Conception du chemin de données et de contrôle d’un microprocesseur RISC 32 bits à cycle

unique.

Encadrants

F. Thiebolt.

D. Dragomirescu

2

Table des matières

I. Introduction .................................................................................................................................. 4

II. Le processeur RISC R3000 ........................................................................................................... 4

III. Présentation du Projet .................................................................................................................. 7

Cahier des charges............................................................................................................................... 7

Travail demandé : ................................................................................................................................ 8

IV. Conception .................................................................................................................................... 8

Le pipeline ........................................................................................................................................... 8

Les aléas .............................................................................................................................................. 8

Conception des différents parties du microprocesseur ...................................................................... 9

Conception et simulation du banc de registre ...................................................................................... 9

Conception et simulation du banc mémoire .......................................................................................10

Définition des fonctions et procédures du microprocesseur RISC. ................................................... 11

Procédure contrôle .............................................................................................................................12

Procédure ALU : ................................................................................................................................13

Procédure envoi : ...............................................................................................................................13

Procédure aléa : ..................................................................................................................................14

Fonction plus : ....................................................................................................................................15

Définition des registres pipeline .........................................................................................................15

Conception du chemin de données ................................................................................................. 15

Les étapes de conception du chemin de données. ..............................................................................15

Analyse comportementale du processeur RISC. ................................................................................16

V. Simulation du processeur ............................................................................................................ 19

VI. Synthèse du microprocesseur RISC ............................................................................................ 23

VII. Conclusion ............................................................................................................................. 26

VIII. 1- Définition du package ........................................................................................................ 28

IX. 2- Code VHDL du microprocesseur RISC ..................................................................................... 40

3

Préambule

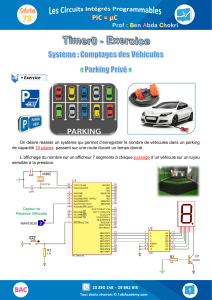

Ce projet est réalisé dans le cadre de l’UE fondamentale Architecture avancés des machines

informatiques de la formation master professionnel conception des architecture des machines et

système informatiques (CAMSI). Le but de ce projet est concevoir un microprocesseur RISC 32bits

intégrant la technologie du pipelining. Ce projet inclue les étapes de conception en VHDL les étapes

de simulations et les étapes de synthèse du microprocesseur en circuit numériques.

4

I. Introduction

Un processeur RISC est un microprocesseur à jeu d'instruction réduit (du mot anglais: reduced

instruction-set computer).C'est un type d'architecture matérielle de microprocesseurs, qui se caractérise

par un jeu d'instructions facile à décoder et comportant uniquement des instructions simples. Le but de

ce projet est de concevoir un microprocesseur RISC pipeliné à chemin de données et de contrôle à

cycle unique. Le déroulement du projet s'articule sur quatre étapes:

• La première étape a consistera à concevoir tous les éléments combinatoires et d'états tels

que l'unité arithmétique et logique (ALU), le banc de registre et le banc mémoire.

• La deuxième étape consistera à concevoir le chemin de données et l'unité de contrôle.

• La troisième étape consistera en la création des fichiers de test pour la simulation et

validation des différents composants du processeur.

• En fin la dernière étape consistera en la synthèse et à l'implémentation du processeur RISC

dans une cible de type ASIC conçu en technologie AMS 0.35µm.

II. Le processeur RISC R3000

Un microprocesseur RISC a les propriétés suivantes :

• Un cycle d’instructions (nombre de cycle d’horloges) identiques à 80% des instructions.

• Les instructions ont la même taille dans notre cas 32 bits.

• Un jeu d’instruction réduit environ 128 instructions.

• formats d’instructions.

• Les accès mémoire se font avec les instructions de types load et store.

• Toutes les opérations excepté les load et store sont de type registres à registres

• L’unité de contrôle du microprocesseur RISC est directement câblée au niveau matériel.

• Une large panel de registres (32 registres de 32 bits).

Taille du

champ 6 bits 5 bits 5 bits 5 bits 5 bits 6 bits Commentaires

Format R OP RS RT RD VALDEC fonction Instruction de type

arithmétique ou logique

ou registre

Format I OP RS RT Immédiat/Adresse Instruction de type

branchement ou immédiat

Format J OP Adresse Instruction de type saut

Tableau 1: les types de formats du jeu d’instructions RISC

5

Le champ OP : code opération sur 6 bits représente la nature du traitement à effectuer

Le champ RS : formé de 5 bits, représente toujours un numéro du registre source

Le champ RT formé de 5 bits, représente un numéro de registre (source ou destination) ou une

condition de branchement.

Le champ RD : formé de 5 bits, représente le numéro de registre de destination.

Le champ VALDEC : formé de 5 bits représente le nombre de décalage dans les instructions de

décalage.

Le champ fonction : formé de 5 bits permet de différencier certaines instructions ayant le même code

opération.

Le champ immédiat : formé de 16 bits représente soit un déplacement signé dans le cas des

instructions de branchement, ou une constante signée immédiate dans le cas des opérations

arithmétiques signées, ou une constante non signée immédiate dans le cas des opérations logiques et

arithmétiques non signées.

Le champ adresse : représente une adresse sur 26 bits.

Le jeu d’instruction est montré dans le Tableau 2 :

Instruction Op Fonction

Lsl 000000 0 Rt Rd ValDec 000000

Lsr 000000 0 Rt Rd ValDec 000010

Jr 000000 Rs 0 0 0 001000

Add 000000 Rs Rt Rd 0 100000

Addu 000000 Rs Rt Rd 0 100001

Sub 000000 Rs Rt Rd 0 100010

Subu 000000 Rs Rt Rd 0 100011

And 000000 Rs Rt Rd 0 100100

Or 000000 Rs Rt Rd 0 100101

Xor 000000 Rs Rt Rd 0 100110

Nor 000000 Rs Rt Rd 0 100111

Slt 000000 Rs Rt Rd 0 101010

Sltu 000000 Rs Rt Rd 0 101011

Jarl 000000 Rs 0 Rd 0 001001

Bltz 000001 Rs 00000 Déplacement signé

Bgez 000001 Rs 00001 Déplacement signé

Bltzal 000001 Rs 10000 Déplacement signé

bgezal 000001 Rs 10001 Déplacement signé

J 000010 Adresse

Jal 000011 Adresse

Beq 000100 Rs Rt Déplacement signé

Bne 000101 Rs Rt Déplacement signé

Blez 000110 Rs 0 Déplacement signé

Bgtz 000111 Rs 0 Déplacement signé

Addi 001000 Rs Rt* Constante signée (sign_extend)

Addiu 001001 Rs Rt* Constante signée (sign_extend)

Slti 001010 Rs Rt* Constante signée (sign_extend)

Sltiu 001011 Rs Rt* Constante signée (sign_extend)

Andi 001100 Rs Rt* Constante signée (sign_extend)

Ori 001101 Rs Rt* Constante non signée (zero_extend)

Xori 001110 Rs Rt* Constante non signée (zero_extend)

Lui 001111 0 Rt* Constante non signée (zero_extend)

Lb 100000 RS** Rt* Déplacement signé

Lh 100001 RS** Rt* Déplacement signé

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

1

/

47

100%