TP de CONVERSION de l`ENERGIE

INSA de Toulouse 4ème année AE

Département Génie Electrique et Informatique Année 2009-2010

TP de CONVERSION de l'ENERGIE

Citation à méditer : « L'électronique de puissance ne peut être qu'une électronique de

commutation » (Guy Séguier).

Objectifs du TP : Concevoir et réaliser une cellule de hacheur dévolteur (ou d'onduleur), ainsi que

son circuit de commande qui met en œuvre le principe de la Modulation de Largeur d'Impulsion.

Les concepts que l'on vous demandera d'acquérir sont les suivants :

●Comprendre le fonctionnement de la brique de base d'un convertisseur statique : la cellule

de commutation.

●Savoir analyser les phénomènes présents lors de la commutation.

●Savoir bien distinguer les différentes échelles temporelles : durée de la commutation / de la

période de découpage / de la période du signal modulant.

Planning prévisionnel : (donné à titre indicatif)

Séance 1 Séance 2 Séance 3 Séance 4

Étude du hacheur

dévolteur

(Commande directe par le

GBF)

Insertion de l'étage driver

de MOS + essais.

Câblage du générateur de

signaux triangulaires.

Étude de la MLI. Mesure

de la valeur de

l'inductance.

Mise en oeuvre de la sonde

différentielle de tension.

Étude de la structure en

pont complet : hacheur 4

quadrants et onduleur de

tension.

Evaluation du travail effectué en TP :

●Fiche de mesure (1 par binôme) à remettre en fin de 4ème séance.

●Un examen écrit (questionnaire TP) individuel, sur table, et sans document, à l'issue des 4

séances, accolé au contrôle final de conversion d'énergie.

Organisation générale du circuit de conversion à réaliser :

Signal

modulant

Porteuse

triangulaire

+

_

GBF

Constant

(cas du hacheur)

Sinusoïdal

(cas de l'onduleur)

0 1

ou

E=20V Charge RL

ou moteur CC

Signal de commmande MLI (TTL)

0V

5V

Alimentation DC

Figure 1 : synoptique général du montage à réaliser.

La charge connectée au hacheur dévolteur sera soit du type R-L, soit un moteur à courant continu.

JM. DORKEL, M. AIMÉ 1/6

INSA de Toulouse 4ème année AE

Département Génie Electrique et Informatique Année 2009-2010

I] Etude du hacheur dévolteur :

Concevoir puis réaliser un bras de hacheur dévolteur à l'aide des éléments fournis :

●une charge R-L série,

●une carte support de composants de puissance,

●un module de transistor MOS,

●un module de diode de commutation.

I.1] Commande directe du transistor MOS par le GBF :

Commander tout d'abord le transistor MOS avec un signal carré 0-10V, à une fréquence de

découpage fdec=20kHz.

1) Observer les formes d'onde de la tension grille-source (notée VGS), de la tension drain-source

(notée VDS), puis du courant dans le transistor (noté iT).

2) Repérer les phases durant lesquelles le transistor est bloqué, et celles où il est passant.

3) Faire varier le rapport cyclique du signal de commande. Quelle est la conséquence sur la

valeur moyenne de la tension VDS, sur la valeur moyenne du courant iT ?

4) Mesurer le temps de montée de la tension VGS. Évaluer la constante de temps

correspondante. Quel est le seuil de VGS à partir duquel le transistor MOS est passant ?

5) Observer l'influence de l'amplitude de la tension de commande sur la mise en conduction du

MOS. Que se passe-t-il si on commande le MOS par un signal carré 0-5V, puis un signal

carré 0-2V ?

6) Observer la différence de potentiel entre 2 points de la piste GND suffisamment éloignés.

Quel est le problème rencontré ? Sous quelle condition peut-on considérer qu'un fil (ou une

piste de circuit imprimé) est une équipotentielle ?

I.2] Insertion d'un étage driver de MOS :

Afin d'optimiser la mise en conduction du transistor MOS, ainsi que son blocage, on souhaite

insérer un étage « driver » entre la grille de ce dernier et le GBF. Le signal de commande délivré

par le GBF sera cette fois-ci choisi au format standard TTL : un créneau 0-5V. Le but de l'étage

d'interfaçage est de permettre une charge et une décharge plus rapide de la capacité parasite d'entrée

du MOS (capacité grille-source notée Ciss , voir figure 2).

Ciss

G

D

S

10Ω

47kΩ

Figure 2 : module de transistor MOS avec sa diode interne.

7) Concevoir et câbler sur plaque d'essai l'étage driver. On pourra utiliser au choix soit une

structure de type push-pull, soit une structure de type totem-pôle à trois transistors

bipolaires.

JM. DORKEL, M. AIMÉ 2/6

INSA de Toulouse 4ème année AE

Département Génie Electrique et Informatique Année 2009-2010

8) Observer le bénéfice obtenu par l'ajout du driver. Comment ont évolué les formes d'onde de

VGS, de VDS ? Les temps de commutation se sont-ils améliorés ?

9) Observe-t-on des phénomènes indésirables dus au fait que les commutations sont plus

rapides ?

I.3] Réalisation d'une commande modulée en largeur d'impulsion :

La modulation de largeur d'impulsion (MLI) est une stratégie qui permet de faire varier le rapport

cyclique des créneaux de tension observé aux bornes de la charge. Il est ainsi possible de moduler la

valeur moyenne glissante de cette tension. Cette propriété sera utilisée lors de la dernière partie de

ce TP (réalisation d'un onduleur monophasé).

La MLI est basée sur le principe d'un signal périodique triangulaire, dont la fréquence fixe celle des

commutations du hacheur. On note fdec cette fréquence de découpage. Le signal triangulaire est

comparé au signal modulant basse fréquence (fmod << fdec).

●Lorsque le modulant est supérieur à la porteuse triangulaire, alors la tension de commande

du MOS est à l'état haut (Vcde=+5V).

●Inversement, lorsque le modulant est inférieur à la porteuse triangulaire, alors la tension de

commande du MOS est à l'état bas (Vcde=0V).

10) Concevoir et câbler sur plaque d'essai un générateur de signaux triangulaires, de fréquence

fdec=20kHz, et d'amplitude 10V crête à crête. On pourra utiliser un AO dual intégré dans le

même boîtier (TL072 ou TL082). Le montage sera alimenté par une tension symétrique de

±15V.

11) Câbler le comparateur tout ou rien. On utilisera un comparateur rapide tel que le LM311.

12) Observer le fonctionnement du hacheur commandé en MLI. Choisir pour cela un signal

modulant de très faible fréquence (fmod < 1Hz). Visualiser la porteuse triangulaire et le signal

de commande du transistor MOS. Comment évolue le rapport cyclique de la tension de

commande lorsque le signal modulant augmente ? Même question lorsqu'il diminue ?

13) Représenter l'allure du courant dans la charge obtenue pour un rapport cyclique égal à 20%,

puis pour un rapport cyclique égal à 80%.

14) Mesurer l'ondulation du courant (crête à crête) obtenue pour un rapport cyclique égal à 50%.

En déduire la valeur de l'inductance de la bobine utilisée.

JM. DORKEL, M. AIMÉ 3/6

INSA de Toulouse 4ème année AE

Département Génie Electrique et Informatique Année 2009-2010

II] Test et mise en oeuvre d'une sonde différentielle de tension :

La sonde différentielle de tension doit permettre de mesurer une différence de potentiel entre deux

points du circuit de puissance. Elle permet de s'affranchir du problème de conflit de masses, que

l'on rencontre lorsque les deux masses des deux sondes d'oscilloscope sont branchées en deux

points de potentiels différents. On peut également utiliser la sonde différentielle pour observer

l'allure du courant dans la charge, en sortie de l'onduleur, comme indiqué sur le schéma de la figure

3. La résistance de mesure vaut Rmes= 0,5Ω. Le composant actif utilisé dans cette sonde est un

INA111. Il s'agit d'un amplificateur d'intrumentation rapide (bande passante et slew-rate élevés) à

gain réglable par un potentiomètre.

15) Tester tout d'abord la sonde différentielle en observant un signal carré (TTL) à 20kHz issu

d'un GBF. Mesurer le slew-rate (dVs/dt). Comparer le slew-rate mesuré avec celui annoncé

dans la documentation technique de l'INA111.

16) Le potentiomètre RG de l'INA111 permet de faire varier le gain de l'amplificateur

d'instrumentation. Faire varier le gain en jouant sur RG.

●Observer le phénomène de dépassement (overshoot) lorsque le gain de l'INA111 est faible.

●Observer l'effet indésirable du slew-rate lorsque le gain de l'INA111 est plus élevé.

●Conclure sur la nécessité d'un compromis sur la valeur du gain. On règlera dorénavant le

potentiomètre sur cette valeur optimale de gain. Mesurer dans cette condition le coefficient

d'amplification de la sonde différentielle.

17) Concevoir une méthode qui permette de mesurer expérimentalement le taux de réjection de

mode commun du montage.

18) Régler le potentiomètre Rp de manière à minimiser le gain de mode commun de la sonde

différentielle.

19) Déterminer le taux de réjection de mode commun pour différentes fréquences.

20) Observer la forme de la tension VS(t) en réponse à une tension de mode commun de forme

rectangulaire et de fréquence 20kHz. Analyser et interpréter vos observations.

AB

VS

R0

+

_

INA111

Rmes ICH

R1

R2

R3

B'

A'

RG

RP

VA-VB= Rmes*ICH

Valeur des composants :

Rmes= 0,5Ω

R0= 30kΩ (résistance à 1%)

R1= 10kΩ (résistance à 1%)

R2= 30kΩ (résistance à 1%)

R3= 10kΩ (résistance à 1%)

Rp= 1kΩ

RG=100kΩ

oscilloscope

Figure 3 : schéma de principe de la sonde différentielle

(application à la visualisation du courant dans la charge).

JM. DORKEL, M. AIMÉ 4/6

INSA de Toulouse 4ème année AE

Département Génie Electrique et Informatique Année 2009-2010

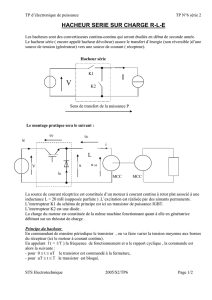

III] Etude du hacheur en pont complet :

III.1] Hacheur en pont complet :

L'étude portait jusqu'à présent sur une structure de hacheur en demi-pont qui permet uniquement

d'obtenir une tension de signe constant aux bornes de la charge. Lorsque l'on désire avoir une

réversibilité en tension (par exemple pour pouvoir inverser le sens de rotation d'un moteur à courant

continu), il est nécessaire de passer à une structure en pont complet. Celle-ci est obtenue en insérant

la charge entre deux cellules de commutation (voir figure 4). Grâce à des interrupteurs

bidirectionnels en courant, on obtient finalement à la fois la réversibilité en tension et en courant au

niveau de la charge. Pour cette raison, le hacheur que l'on vous propose de câbler ici s'appelle

également hacheur quatre quadrants.

21) Câbler le deuxième bras de hacheur de manière à obtenir un hacheur 4 quadrants. Insérer les

deux drivers dédiés à la commande de chacun des deux bras. Pour les questions 21 à 24, on

utilisera la charge RL.

22) Câbler la commande MLI du deuxième bras de hacheur. On pourra réutiliser le signal

triangulaire généré dans la question 10, et lui adjoindre un deuxième comparateur de type

LM311 (voir figure 4).

23) Observer les signaux de commande des 2 cellules de commutation. Vérifier qu'ils sont bien

complémentaires.

24) Observer la tension Uch aux bornes de la charge, ainsi que le courant ich qui entre dans celle-

ci. Faire varier la tension de consigne Vcons, et observer l'effet induit sur Uch et ich . Tracer les

formes d'onde correspondantes sur la feuille de mesure. Exprimer Uch en fonction de la

tension d'alimentation E et du rapport cyclique

α

2 qui caractérise le fonctionnement de K2

(voir figure 4).

25) Placer un moteur à courant continu (à aimants permanents) en guise de charge. Vérifier que

l'on peut contrôler à loisir sa vitesse de rotation, ainsi que son sens de rotation.

Tension

de

consigne

Porteuse

triangulaire

Vcons +

_0 1 Signal de

commmande 1

MLI (TTL)

E=20V

M

DRIVER 1

DRIVER 2

+

_0 1

LM311

LM311 Signal de

commmande 2

MLI (TTL)

ich

Uch

Cellules de commutation

K1

K2

K3

K4

Figure 4 : structure de hacheur en pont complet

(utilisation pour la commande d'un moteur à courant continu)

JM. DORKEL, M. AIMÉ 5/6

6

6

1

/

6

100%