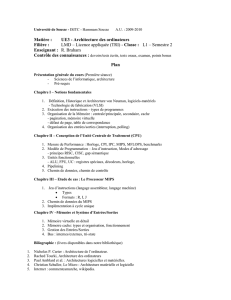

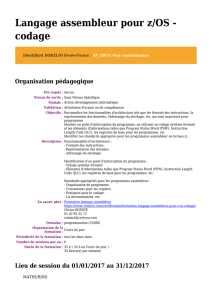

Conception et exploitation des processeurs

Conception et exploitation des processeurs

Chargé de cours : Frédéric Pétrot

Équipe pédagogique :

Stéphane Mancini, Luc Michel, Olivier Muller,

Christophe Rippert, Sebastien Viardot

Année universitaire 2012-2013

Conception et exploitation des processeurs

Introduction

Introduction

Étude du langage d’assemblage de 2processeurs

Intel x86_64 (AMD64, CoreIx)

Évolution de l’ISA hégémonique pour desktops, laptops et serveurs

Constructeur Intel a, compatibilité ascendante depuis 1979

Machine avec ISA CISC : Complex Instruction Set Computer

a.www.intel.com

MIPS R3000

ISA symbolique RISC : Reduced Instruction Set Computer

Constructeur MIPS a, 1988

Importante part de marché dans l’embarqué (networking en

particulier), mais nettement moins que ARM b, favori des

smartphones et autres tablettes.

a.www.mips.com

b.www.arm.com

4 / 30

Conception et exploitation des processeurs

Introduction

Introduction

CISC Intel x86_64

jeu d’instruction « prolifique », près de 500 instructions

destiné à être programmé par un humain

vise un code « compréhensible » et dense

nombreux modes d’adressage

opérandes peuvent être des cases mémoire

bonne partie des registres spécialisés par le matériel

cherche à optimiser la taille du programme par l’utilisation

d’instructions complexes

5 / 30

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

1

/

30

100%