Documentation étoffée

1

Am2900 et Manuel d’utilisation du simulateur

Emu2900

(Version 0.2, 029-Octobre-2008)

Par Mohamed Boussamma

mohamed-dhia.boussamma.1@ulaval.ca

Département GEL-GIF

Faculté de sciences et génie

Université Laval

2

1-Introduction :

La famille des circuits intégrés Am2900 à été conçue par AMD (Advanced Micro Devices) en

1975, à cette époque AMD à mis sur le marché plusieurs modules basés sur la technique du

‘Bit Slice’, parmi les circuits intégrés, on cite les suivants : Am2901 (ALU 4 bits), Am2904

(Control de statut et des shifts), Am2910 (séquenceur CCU 12 bits). Ces circuits intégrés tout

ensemble constituent un système minimum complet. Il existe cependant beaucoup

d’extensions comme le Am2914 (contrôleur d’interruption) par exemple. Une bonne

technologie ?’ Ce que l’on sait, c’est que cela est à partir du PDP-10, basé sur les circuits

intégrés AM2900, que Bill Gates et Paul Allen ont lancé la révolution de l’informatique que

nous connaissons !

Pour la culture générale :

http://www.dailymotion.com/videos/relevance/search/cinglés+de%20l'informatique/1

http://youtube.com/results?search_query=pirates+of+silicon+valley

La famille Am2900 est un bon moyen d’apprentissage pour l’introduction au domaine des

microprocesseurs microprogrammés, et son apprentissage ne demandera pas beaucoup de

temps. Afin de faciliter votre apprentissage, le simulateur Emu2900 à été développé pour le

cours GIF-17456, ce simulateur reprend le fonctionnement exact d’une version légèrement

modifiée de l’ALU 2901 (8 bits au lieu de 4), du CCU Am2910, de l’Am2904 complémentée

par une mémoire programme, un Registre d’instruction (IR) et une mémoire Mapping

PROM.

Le simulateur fonctionne sous Windows XP, mais le test sur Vista n’a pas encore été

effectué, le code du simulateur est sous licence GPL (http://www.gnu.org/licenses/gpl.html)

et le code source vous sera fournis sur demande, il suffit juste de me contacter.

3

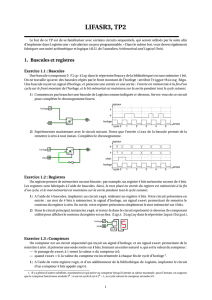

2-Architecture du système :

L’architecture de la version modifiée du système est présentée dans la figure ci-dessous

Figure 1- Architecture génerale du système

4

Lorsque l’on fait exécuter un programme, chacun des modules du simulateur entrent en

fonction. Au départ, on doit effectuer un reset général du système, qui permet

d’initialiser tous les signaux à zéro, et d’aller à la routine FETCHINSTR dans le

microprogramme.

C’est à chaque montée d’horloge, que le pipeline envoie de nouveaux signaux de contrôle

aux différents modules pour l’instruction suivante. Ces signaux se retrouvent à l’entrée

du pipeline, et sont remplacés par de nouvelles valeurs suite à la montée d’horloge. Ces

valeurs proviennent en réalité de la micromémoire, et représentent les différentes valeurs

de la série de bits qui forment une microinstruction. À chaque adresse de la

micromémoire, on retrouve une microinstruction. Les microinstructions non

programmées contiennent donc une série de bits qui ont tous la valeur zéro. Programmer

une microinstuction correspond donc à déterminer la valeur de ces différents bits.

Comme il l’a été mentionné précédemment, ce sont la valeur de ces différents bits qui

contrôlent les différents modules du simulateur. Chaque microinstruction contient donc

71 signaux de contrôles. Ces signaux de contrôles sont divisés en instructions,

dépendamment du module qu’ils contrôlent. Chaque instruction est divisée en champs,

dépendamment de quelle section du module elle contrôle. Cette division améliore la

programmation de ces signaux.

Le pipeline permet donc d’afficher les signaux de contrôle pendant un cycle d’horloge.

Cela assure donc la stabilité du système. C’est donc pendant ce cycle d’horloge que le

microséquenseur AM2910 détermine l’adresse de la prochaine microinstruction et que le

AM2901 (l’Alu), effectue les différentes opérations déterminées par les signaux de

contrôle sortant du pipeline. Toutes les opérations du microséquenseur AM2910, du

AM2901 et de la macromémoire doivent dont s’effectuer en un cycle d’horloge. Car à la

prochaine montée d’horloge, ce sont les signaux de la prochaine microinstruction qui

seront affichés à la sortie du pipeline. Normalement, l’accès à la macromémoire se fait

en plus d’un cycle d’horloge, mais pour faciliter la simulation, cet accès se fera en un

coup d’horloge. C’est pourquoi certains modules réagiront à la descente d’horloge.

Une instruction machine est composée de plusieurs microinstructions, et ces

instructions se retrouvent dans la macromémoire, avec les données nécessaires à

l’exécution du programme. Un programme contient plusieurs instructions machines.

Une table de correspondance permet de déterminer la première microinstruction d’une

instruction machine.

Dans ce qui suit on va expliquer le fonctionnement de chaque partie du système.

2-1- La macromémoire :

La macromemoire est la mémoire principale que le système utilise pour exécuter les

instructions en code machine, cette mémoire peut stocker jusqu'à 32 données de 8 bits

(32x8). La macromémoire est connectée au MAR, au MBR ainsi que le D-BUS. Les opérations

de lecture de la mémoire se fait sans aucun délai, mais l’écriture se fait à la descente de

l’horloge. Ceci est expliqué plus tard.

La lecture/écriture de mémoire est contrôlé par deux bits de contrôle RDWR (00 : aucune

opération, 01 : écrire la mémoire, 10 : lire la mémoire)

5

2-2- Le MAR:

Le MAR (Memory Address Register) est directement connecté aux lignes de sélection

d’adresse de la macromémoire, le MAR est un Latch qui mémorise l’adresse à la montée de

l’horloge, cela veut dire que le MAR sera rempli par la nouvelle donnée avant que la

donnée dans le MBR sera écrite dans l’adresse indiquée par le MAR.

Vu que la macromémoire est composée de 32 cases, seulement 5 bits du MAR sont utilisés

pour adresser cette dernière, donc les 3 bits de poids le plus haut sont sans importance.

X

X

X

A4

A3

A2

A1

A0

Figure-2- Le registre MAR

L’accès au MAR est effectué à partir de du Bus principal (D_BUS) quand le bit d’activation

(load) est à 1 sinon aucune valeur n’est inscrite, ce bit peut être codé dans le champ OFFOF

de la micromémoire (b1).

2-2- Le MBR:

Le MBR (Memory Buffer Register) est un registre qui sert d’interface avec la mémoire, le

MBR contient une entrées, une sortie et un bus bidirectionnel (entre le MBR et la

macromémoire), l’entrée provient du Bus principal (dans le cas ou on veut écrire dans la

macromémoire), le bus bidirectionnel est connecté à la macromémoire et la sortie est

connectée vers le bus principal et isolée par un buffer tri-state.

Pour écrire dans le MBR à partir du bus principal, on met le bit load à 1 (b0 du champ

OFFOF), si on veut écrire dans le MBR à partir de la macromémoire on met les bits RDWR à

10, et si on veut mettre la donnée du MBR dans le bus principal on met le champ ONTO à

001, Il est aussi possible de mettre directement la donnée de la macromémoire dans le bus

en jouant sur OFFOF et ONTO.

2-2- Le Registre d’instructions IR:

Le registre IR est un latch de 16 bits divisé en IR_MSB et IR_LSB, qui mémorise l’instruction à

exécuter qui provient de la macromémoire.

IR_MSB : l’entrée est connectée avec le D_BUS et contrôlé par b2 du champ OFFOF, la sortie

est connectée vers le MappingProm. Ce registre sert principalement à mémoriser l’opcode

de l’instruction qui sera convertie en adresse de début dans la micromémoire par

l’intermédiaire du MappingProm.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

1

/

25

100%