1. Principe du I2C

Principe du I2C Page 1

Cours 243-648 Communications Numériques A-08

Le bus I2C

Claude Barbaud 4 septembre 2008

1. Principe du I2C

Le I2C (Inter Integrated Circuit) est un bus série synchrone multi-maître qui

fonctionne sous la relation maître-esclave.

Développé par Philips. Géré par l’I2C bus comitee.

Maître-esclave

C’est le maître qui contrôle la communication, qu’il soit l’émetteur ou le

récepteur des données.

L’esclave est alors soumis au maître : il reçoit ou envoie des données sur

demande. La synchronisation est faite par le maître.

Série synchrone

Les communications sont synchronisées par une horloge (fournie par le

maître).

Multi-Maître

Plusieurs processeurs peuvent prendre le contrôle du bus. Le protocole

prévoit une procédure de prise de contrôle du bus.

3 fils

une horloge (SCL),

une ligne de données (SDA),

un commun.

Principe du I2C Page 2

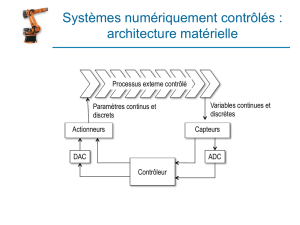

2. Hardware

La configuration du bus I2C est très simple : toutes les sorties sont à

collecteur ouvert ou à drain ouvert, et la logique est positive.

Par cette configuration, les lignes sont au niveau logique 1 au repos, sans

qu’aucun circuit ne place cette ligne à 1.

Il est nécessaire de placer des résistances de rappel (pull-up) pour définir

le niveau haut.

Le nombre de composants qu'il est possible de relier est limité par la

charge capacitive des lignes SDA et SCL : 400 pF . Un composant a une

charge entre 10 et 20 pF.

Les données sont transmises en série à 100Kbits/s en mode standard et

jusqu'à 400Kbits/s en mode rapide.

Une impulsion d’horloge est générée à chaque fois qu’un bit est transféré.

Pas de court-cicuit possible sur SDA et SCL.

3. Protocole logiciel

Avec le compilateur CCS

On doit placer la directive #use au début du fichier

#use i2c(master, SDA = PIN_C4, SCL = PIN_C3)

Au repos

Les lignes SDA et SCL sont au niveau haut (1 logique).

Condition de départ

Un processeur (maître) signale son intention de parler par la condition

START:

Il place SDA = 0 pendant que SCL est au repos (=1)

Le bus est alors occupé: les autres ne peuvent plus parler.

Principe du I2C Page 3

Avec le PIC: i2c_start();

Condition d'arrêt

Le processeur (maître) arrête de parler en replaçant la ligne SDA à 1

pendant que SCL est au repos ( = 1)

Le bus est alors libre: les autres peuvent parler

Avec le PIC: i2c_stop();

En activité

Les changements sur SDA ont lieu pendant que SCL = 0.

Format des transferts

Les données sont transférées en bytes. Le bit le plus important est envoyé

en premier.

1. On envoie d'abord l'adresse du périphérique. Cette adresse est sur 7

bits [A7..A1]

Le 8ème bit est le R/W: 0 = Write, 1 = Read.

Avec le PIC: i2c_write(adresse);

Des parties d'adresse sont déterminées d'avance pour un type de

périphérique. Les autres parties sont déterminées par matériel (état de

broches)

Liste partielle de périphériques

Principe du I2C Page 4

Principe du I2C Page 5

6

6

7

7

8

8

9

9

1

/

9

100%