_______________________________________________________________________________________________

Technical Specification

Industrial Compact Flash Card

Release Date: June 2005

Version: 1.4

_______________________________________________________________________________________

SCM PC-Card GmbH

Sperl-Ring 4

D-85276 Pfaffenhofen

Tel: +49 8441 788 810

Fax: +49 8441 788 900

www.scm-pc-card.de

S-CN CompactFlash Card Industrial Application

TCADO-SCF-000018.4 1/139 0605V4

Preliminary

S-CN CompactFlash Card

Industrial Application

Product Specification

June 2005

S-CN : Single-Level-Cell-NAND

S-CN CompactFlash Card Industrial Application

TCADO-SCF-000018.4 2/139 0605V4

Document History

Version Description Date Approved by

1 New issue Apr. 2004 Debby Chang

2

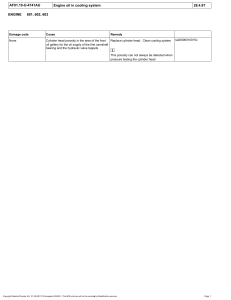

1. Supported flash kind for block

size.

2.Capacity appearance modify

3.Checking Product UDMA

function (announce not supported

multi word DMA)

August. 2004 Xeras Xiang

3 1.Update AC Characteristics December 2004 Ethan Cheng

4

1. Power Consumptions

2. Environment conditions

3. MTBF

4. R/W Test

5. Temp Flow Chart

6. PCB No

June 2005 Verlaine Lin

S-CN CompactFlash Card Industrial Application

TCADO-SCF-000018.4 3/139 0605V4

Contents

INDUSTRIAL APPLICATION.............................................................................................................................................................................1

1. INTRODUCTION.........................................................................................................................................................................................7

1.1 GENERAL DESCRIPTION ........................................................................................................................................................................7

1.2 FEATURES...............................................................................................................................................................................................8

2. PRODUCT SPECIFICATION...................................................................................................................................................................9

2.1 OPERATION AND ENVIRONMENT DESCRIPTION ....................................................................................................................................9

2.2 PHYSICAL DESCRIPTION ......................................................................................................................................................................10

3. PRODUCT MODEL..................................................................................................................................................................................11

3.1 PART NUMBER DEFINITION.................................................................................................................................................................11

4. SUPPORT FLASH MEDIA......................................................................................................................................................................12

4.1 SUPPORTED NAND FLASH TYPE .......................................................................................................................................................12

4.2 LOGICAL FORMAT PARAMETERS (CHS)............................................................................................................................................12

5. BLOCK DIAGRAM...................................................................................................................................................................................14

5.1 CONTROLLER ARCHIVE.......................................................................................................................................................................14

5.2 FLASH CARD ARCHIVE........................................................................................................................................................................14

6. SPECIFICATION AND FEATURES.....................................................................................................................................................15

6.1 ELECTRICAL SPECIFICATION ...............................................................................................................................................................15

6.1.1 Absolute Maximum Ratings..........................................................................................................................................................15

6.1.2 General DC Characteristic...........................................................................................................................................................15

6.1.3 DC Electrical Characteristics for 5 Volts Operation..................................................................................................................15

6.1.4 DC Electrical Characteristics for 3.3 Volts Operation...............................................................................................................16

6.1.5 Attribute Memory Read Timing Specification.............................................................................................................................16

6.1.6 Configuration Register(Attribute Memory)Write Timing Specification ....................................................................................17

6.1.7 Common Memory Read Timing Specification.............................................................................................................................17

6.1.8 Common Memory Write Timing Specification............................................................................................................................18

6.1.9 I/O Input (Read) Timing Specification.........................................................................................................................................19

6.1.10 I/O Input (Write) Timing Specification ...................................................................................................................................20

6.1.11 True IDE Mode I/O (Read/Write) Timing Specification........................................................................................................21

6.1.12 True IDE Ultra DMA Mode I/O (Read/Write) Timing Specification...................................................................................23

6.1.12.1 Ultra DMA Data-In Burst Initiation Timing............................................................................................................................................ 24

6.1.12.2 Sustained Ultra DMA Data-In Burst Timing........................................................................................................................................... 25

6.1.12.3 Ultra DMA Data-In Burst Host Pause Timing........................................................................................................................................ 25

6.1.12.4 Ultra DMA Data-In Burst Device Termination Timing.......................................................................................................................... 26

S-CN CompactFlash Card Industrial Application

TCADO-SCF-000018.4 4/139 0605V4

6.1.12.5 Ultra DMA Data-In Burst Host Termination Timing.............................................................................................................................. 26

6.1.12.6 Ultra DMA Data-In Burst Host Termination Timing.............................................................................................................................. 27

6.1.12.7 Sustained Ultra DMA Data-Out Burst Timing........................................................................................................................................ 27

6.1.12.8 Ultra DMA Data-Out Burst Device Pause Timing................................................................................................................................. 28

6.1.12.9 Ultra DMA Data-Out Burst Device Termination Timing....................................................................................................................... 28

6.1.12.10 Ultra DMA Data-Out Burst Host Termination Timing........................................................................................................................... 29

6.2 POWER MANAGEMENT .......................................................................................................................................................................29

6.2.1 Normal Mode.................................................................................................................................................................................29

6.2.2 Power down Mode ........................................................................................................................................................................29

6.3 PHYSICAL SPECIFICATION ...................................................................................................................................................................30

6.3.1 CompactFlash CF Type I..............................................................................................................................................................30

6.3.2 CompactFlash CF Type II.............................................................................................................................................................30

7. PIN ASSIGNMENT....................................................................................................................................................................................31

7.1 COMPACTFLASH PIN TYPE..................................................................................................................................................................31

7.2 SIGNAL DESCRIPTION..........................................................................................................................................................................33

8. CIS AND FUNCTIONS CONFIGURATION REGISTERS.............................................................................................................38

8.1 CONFIGURATION OPTION REGISTER (200H) .....................................................................................................................................38

8.2 CARD CONFIGURATION AND STATUS REGISTER (ADDRESS 202H).................................................................................................39

8.3 PIN REPLACEMENT REGISTER (ADDRESS 204H) ..............................................................................................................................40

8.4 SOCKET AND COPY REGISTER (ADDRESS 206H) ..............................................................................................................................40

8.5 CARD INFORMATION STRUCTURE (CIS)............................................................................................................................................41

9. ATA SPECIFIC REGISTER DEFINITIONS.......................................................................................................................................55

9.1 MEMORY MAPPED ADDRESSING........................................................................................................................................................55

9.2 CONTIGUOUS I/O MAPPING ADDRESSING .........................................................................................................................................56

9.3 OVERLAPPING I/O MAPPING ADDRESSING........................................................................................................................................57

9.4 TRUE IDE MODE.................................................................................................................................................................................57

9.5 ATA REGISTERS...................................................................................................................................................................................58

9.5.1 Data Register.................................................................................................................................................................................58

9.5.2 Error Register................................................................................................................................................................................58

9.5.3 Feature Register.............................................................................................................................................................................59

9.5.4 Sector Count Register....................................................................................................................................................................59

9.5.5 Sector Number Register................................................................................................................................................................59

9.5.6 Cylinder Low Register...................................................................................................................................................................60

9.5.7 Cylinder High Register..................................................................................................................................................................60

9.5.8 Drive Head Register......................................................................................................................................................................61

9.5.9 Status Register................................................................................................................................................................................62

9.5.10 Alternate Status Register..........................................................................................................................................................62

9.5.11 Device Control Register...........................................................................................................................................................63

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

99

99

100

100

101

101

102

102

103

103

104

104

105

105

106

106

107

107

108

108

109

109

110

110

111

111

112

112

113

113

114

114

115

115

116

116

117

117

118

118

119

119

120

120

121

121

122

122

123

123

124

124

125

125

126

126

127

127

128

128

129

129

130

130

131

131

132

132

133

133

134

134

135

135

136

136

137

137

138

138

139

139

140

140

1

/

140

100%