Logique Séquentielle: Théorie & Guide Pratique pour Électrotechnique

Telechargé par

Abd elouahed Fejjaji

OFPPT

ROYAUME DU MAROC

M

ODULE

N°

19

LOGIQUE

SQUENTIELLE

S

ECTEUR

:

ELECTROTECHNIQUE

S

PECIALITE

:

EM

N

IVEAU

:

Q

UALIFICATION

ANNEE

2010

Office de la Formation Professionnelle et de la Promotion du Travail

D

IRECTION

R

ECHERCHE ET

I

NGENIERIE DE

F

ORMATION

R

ESUME

T

HEORIQUE

&

G

UIDE DE

T

RAVAUX

P

RATIQUES

Résumé de Théorie et

Guide de travaux pratiques Module 19 : Logique sequentielle

OFPPT/DRIF/CDC_GE

1

Document élaboré par :

Nom et prénom EFP DR

Mme PANTAZICA LIVIA CDC - GE

Révision linguistique

-

-

-

Validation

-

-

-

Résumé de Théorie et

Guide de travaux pratiques Module 19 : Logique sequentielle

OFPPT/DRIF/CDC_GE

2

S

OMMAIRE

RESUME THEORIQUE................................................................................................ 7

I. Représantation graphiques d’une séquence ou d’un cycle ..................................... 8

II. Les principaux symboles associés à diverses représentations graphiques d’une

séquence............................................................................................................... 16

III. Modes de marche et d’arrêt d’une séquence......................................................... 16

III.1 Les modes de marche :................................................................................ 16

III.2 Les arrêts :.................................................................................................... 17

IV. Les éléments de mémoires :.................................................................................. 20

IV.1 Concept de mémorisation :........................................................................... 20

IV.3 Les bascules :............................................................................................... 22

V. Les registres:..................................................................Erreur ! Signet non défini.

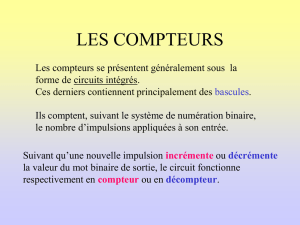

VI. Les compteurs :..................................................................................................... 32

VI.1 Identification de la fonction :...................................................................... 32

VI.2 Les compteurs asynchrones :................................................................... 33

VII.4 Les compteurs synchrones:...................................................................... 37

VII.5 Les compteurs intégrés:............................................................................ 39

GUIDE DE TRAVAUX PRATIQUES........................................................................... 40

Exercices :.................................................................................................................. 41

TP.1 – Essai des bascules élémentaires :.................................................................. 44

TP.2 – Essai des registres à décalage:....................................................................... 48

TP.3 – Essai des compteurs asynchrones:................................................................. 50

TP.4 – Essai des compteurs synchrones:................................................................... 53

Évaluation de fin de module :...................................................................................... 55

Liste bibliographique................................................................................................... 56

Résumé de Théorie et

Guide de travaux pratiques Module 19 : Logique sequentielle

OFPPT/DRIF/CDC_GE

3

MODULE 19 : LOGIQUE SÉQUENTIELLE

Code : EM 19 Durée : 60 h

OBJECTIF OPERATIONNEL

COMPORTEMENT ATTENDU

Pour démontrer sa compétence, le stagiaire doit

appliquer des notions de logique séquentielle

selon les conditions, les critères et les précisions qui suivent.

PRESENTATION

L’objectif de ce module de compétence transversale est de faire acquérir les connaissances

relatives à l’analyse de différentes représentations graphiques d’une séquence, à leur traduction

sous forme de schéma, à la sélection des composants, au traçage de schémas de montage et au

montage d

e circuits de base de logique séquentielle. Il vise donc à rendre le stagiaire apte à

appliquer des notions de logique séquentielle.

CONTEXTE DE REALISATION

• A l’aide :

- de manuels techniques;

- de fiches techniques;

- de composants logiques;

- d’instruments de mesure.

• A partir :

- de directives;

- d’une représentation graphique d’une séquence.

REFERENCES

- Notes de cours

R

ésumé de Théorie et

Guide de travaux pratiques Module 19 : LOGIQUE

SEQUENTIELLE

OFPPT/DRIF/CDC_GE

4

PRECISION

ET

PREALABLES ELEMENTS

DE

CONTENU

A. Avant d’analyser différentes

représentations graphiques d’une

séquence :

- algorithme

- chronogramme

- Grafcet

le stagiaire doit :

1. Décrire les règles de construction

de diverses représentations

graphiques d’une séquence

2. Reconnaître les principaux

symboles associés à diverses

représentations graphiques d’une

séquence

3. Décrire les modes de départ, de

marche et d’arrêt d’une séquence

- Détermination :

• des grandes étapes (action)

• des points d’entrée ou de sortie des

données

• du point de prise de décision

• de l’aspect sécuritaire de la séquence,

etc.

• s’il y a répétition ou arrêt de la séquence,

etc.

- Début ou extrémité de l’ordinogramme.

- Parallélogramme :

• point d’entrée ou de sortie de données

- Rectangle :

• opération sans entrée ni sortie ou

opération mathématique

- Losange :

• indication d’un point de décision

- Petit cercle :

• possibilité de raccorder des segments de

grands programmes

- Carré :

• pour les étapes

- Tiret :

• pour les transitions

- Flèche :

• sens du déplacement

- Insertion de la condition de départ dans un

compteur binaire, à décade et un registre à

décalage :

• manuel

• automatique

- Remise à zéro des compteurs et des registres

- Un automatisme simple

- Un circuit dont l’opération est conditionnel à

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

1

/

56

100%