Ecole Supérieure de Technologie

Département Génie Electrique

Option Electronique et Informatique Industriel

Rapport de Stage de Fin d’Etudes

Sujet

Mise en place d’un système taper au niveau ‘Unloader’

d’un MULTITEST

Date de soutenance : 29/06/2021

Réalisé par : Encadré par :

LHSAINI Soufiane Pr. Fayrouz DKHICHI

Mr. Hicham ROUMED

Année universitaire : 2020-2021

i

Remerciements

C’est avec un grand plaisir que je rédige ces lignes comme signe de gratitude et de

reconnaissance à tous ceux qui ont contribué, de près ou de loin, à l’élaboration de ce

travail. Ainsi je remercie la direction de la société « ST » qui ont accepté de

m’accueillir au sein de son organisme.

Mes vifs remerciements vont à Mr. ROUMED et Pr DKHICHI pour leur

encadrement permanent, leur assistance perspicace ainsi que pour leurs instructions

pertinentes tout au long de ce projet.

Que tout le corps administratif et professoral de l’ESTC trouve ici l’expression de

mes sentiments les plus respectueux.

ii

Sommaire

Introduction Générale ..................................................................................................................... 1

Chapitre 1 : Présentation de ST Microelectronics .............................................................. 2

1.1. Identification de la société ..................................................................................... 2

1.2. ST au Maroc ............................................................................................................... 3

1.3. Produits de ST Bouskoura ...................................................................................... 4

1.4. Processus de fabrication ......................................................................................... 5

1.5. Conclusion ................................................................................................................. 7

Chapitre 2 : Machine Multitest ................................................................................................... 8

2.1. Introduction ............................................................................................................... 8

2.2. Handler Multitest 9308 .......................................................................................... 8

2.3. Partie Hardware ..................................................................................................... 10

2.4. Statistiques des erreurs ......................................................................................... 11

2.5. Problématique .......................................................................................................... 12

2.6. Diagramme d’Ishikawa ......................................................................................... 13

2.7. Conclusion ............................................................................................................... 14

Chapitre 3 : Système Taper ........................................................................................................ 15

3.1 Introduction ............................................................................................................... 15

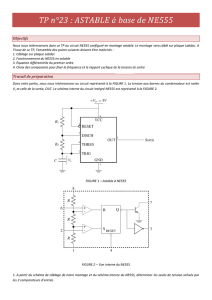

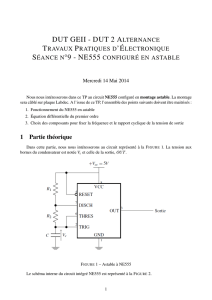

3.2 Circuit NE555 .......................................................................................................... 15

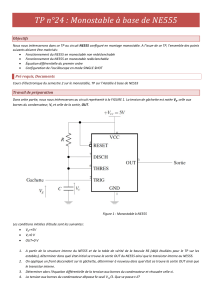

3.3 Le capteur de coincement ..................................................................................... 18

3.4 Schéma global et fonctionnement du système ............................................... 19

3.5 Réalisation ................................................................................................................ 21

3.6 Conclusion ............................................................................................................... 21

Conclusion Générale ...................................................................................................................... 22

Webographie .................................................................................................................................... 23

Annexe : NE555 Datasheet ......................................................................................................... 24

iii

Liste des figures

Figure 1.1 : Implantation de STMicroelectronics dans le monde ………….....……… 2

Figure 1.2 : Graphe des principaux segments de marché .……………………....…… 3

Figure 1.3 : Opération de collage du Wafer …………………………………………. 5

Figure 1.4 : Opération de découpage du Wafer ………………………...………….… 5

Figure 1.5 : Opération du Die-Attach …………………………………….……….… 6

Figure 2.1 : La machine Handler ………………………………….…………….…… 8

Figure 2.2 : Module Unloader ..………………………………………….................... 9

Figure 2.3 : Connexion de l’AutoJig au Test-Head et au Testeur ……….……….… 10

Figure 2.4 : Testeur QT200 …………………………………………...……….…… 10

Figure 2.5 : Test-Head ………………………………...………..…………….…… 11

Figure 2.6 : AutoJig ………………………….………………….…….……….…… 11

Figure 2.7 : Courbe des erreurs au niveau du Unloader …...…………….…….….. 12

Figure 2.8 : Causes du coincement ………………………….….………….....…… 13

Figure 3.1 : NE555 …………………………………………………………….…… 15

Figure 3.2 : Structure interne d’un NE555 ..……………………...……….…...….... 16

Figure 3.3 : Circuit NE555 en mode astable ………………...………….…..……… 17

Figure 3.4 : Détecteur de coincement ………………………..………….….……… 18

Figure 3.5 : Schéma électrique d’un capteur photo-électrique ………………......… 19

Figure 3.6 : Circuit du système ……………….……………...…………….……..… 19

Figure 3.7 : Signal de sortie Q du NE555………………………..………….....…… 20

Figure 3.8 : Réalisation de la carte …………...……………………….………....… 21

SFE : 2020-2021 1 / 30

Introduction Générale

Le marché international des semi-conducteurs fournit divers domaines notamment

l’automobile, les télécommunications, la mécanique et l’aéronautique. Ce marché est

sujet à une grande concurrence mondiale.

ST Microelectronics faisant partie de ce marché, opte pour la bonne qualité de ses

produits. Ainsi, la gestion maitrisée de la production et l’amélioration du rendement

par élimination des pertes et diminution des coûts constituent la démarche

d’excellence durable de ST Microelectronics.

C’est dans cette perspective que s’inscrit mon sujet de stage de fin d’étude effectué

au sein de la société ST Microelectronics, intitulé « Mise en place d’un système taper

au niveau ‘Unloader’ d’un MULTITEST ». Ce projet consiste à réaliser une carte

électronique qui assure la commande d’un taper pour décoincer les pièces.

Ce rapport présente l’intégralité des démarches suivies pour la réalisation de ce

projet. Il est divisé en trois parties qui résument le travail que j’ai fourni au cours de

mon stage :

• Présentation de ST Microelectronics et description de la ligne de production.

• Explication détaillée sur le fonctionnement de la Machine Multitest.

• Etude théorique et réalisation du système taper qui va résoudre le problème du

coincement.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

1

/

30

100%